Najważniejsi inżynierowie AMD przybyli na prestiżowe, coroczne sympozjum Hot Chips, aby przedstawić szczegóły i osiągnięcia inżynieryjne, jakie legły u podstaw wysokiej wydajności i energooszczędności nowych procesorów APU o kodowej nazwie “Carrizo” i nowej rodziny kart graficznych AMD Radeon R9 Fury z rdzeniami “Fiji”. Prezentacje koncentrowały się na szczegółach dotyczących mechanizmów przetwarzania grafiki i wideo wysokiej rozdzielczości w 6. generacji procesorów AMD APU oraz na 8-letniej historii powstania nowej technologii produkcji warstwowych modułów pamięci, jakie obecnie stanowią podstawę dla najwyższej klasy kart graficznych AMD Radeon Serii Fury. Dzięki unikalnej architekturze SoC (System-on-Chip) nowa generacja procesorów AMD Serii A zapewnia nawet o 40% obniżony pobór energii rdzeni x86 przy znaczącym wzroście wydajności w zakresie mocy obliczeniowej, graficznej i multimedialnej w porównaniu z poprzednią generacją procesorów APU. Z kolei nowa karta graficzna AMD Radeon R9 Fury X osiąga 1,5-krotnie lepszą sprawność energetyczną niż topowy model AMD poprzedniej generacji.

Zwieńczeniem technologii warstwowych układów scalonych są topowe karty graficzne

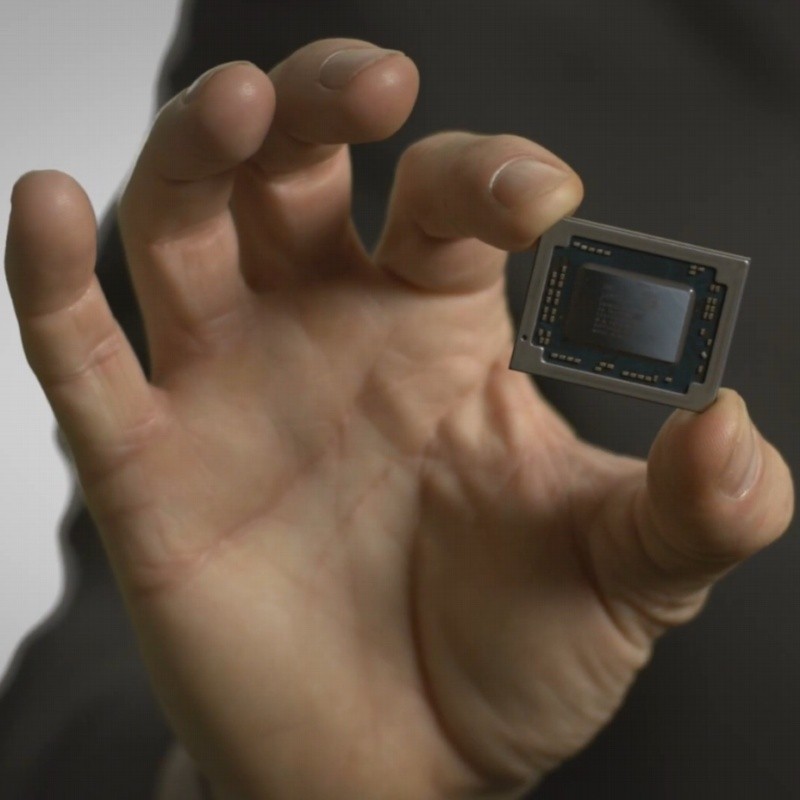

Historia nowej rodziny kart graficznych AMD Radeon R9 Fury miała swój początek wraz odkryciem najlepszej metody produkcji warstwowych układów, aby można było zaopatrzyć procesor graficzny w dużą ilość pamięci umieszczonej w jednym zestawie scalonym i w ten sposób znacząco zwiększyć przepustowość bez podnoszenia zużycia energii. Dzięki współpracy z partnerem z branży pamięci, czyli firmą SK Hynix, nowa, bazująca na architekturze GCN (Graphics Core Next) karta graficzna oferuje do 4 GB pamięci wysokiej przepustowości (HBM, tj. High-Bandwidth Memory) podłączonej przez 4096-bitowy interfejs i tym samym umożliwia osiągnięcie transferów na poziomie aż 512 Gb/s. Ten nowy rodzaj pamięci można było umieścić blisko rdzenia graficznego dzięki zastosowaniu szeregu nowych technologii: pierwszego szerokopasmowego interpozera (przekładki krzemowej), pierwszych wewnątrz-krzemowych linii sygnałowych (TSV, tj. Throigh-Silicon Vias) i mikrozłączy (micro-bumps). HBM wraz z wykorzystanym interpozerem zapewnia 60% wyższą przepustowość i 4-krotnie lepszy współczynnik sprawności energetycznej w porównaniu do poprzedniej generacji pamięci GDDR5. Jednocześnie rodzina układów graficznych “Fiji” jest w stanie dostarczyć 8,6 TeraFlopsa mocy obliczeniowej, co jest o 35% lepszą wartością niż topowe karty graficzne AMD poprzedniej generacji z serii AMD Radeon R9 290. W rezultacie osiągnięto 1,5-krotnie wyższą wydajność w przeliczeniu na 1 Wat pobieranej energii.

Energooszczędność procesorów APU

Nowa, 6. generacja procesorów AMD APU Serii A jest wyposażona w nawet 12 rdzeni obliczeniowych (4 CPU + 8 GPU) wykorzystując rdzenie x86 “Excavator” i trzeciej generacji architekturę AMD GCN. Tak zaprojektowany procesor zapewnia ponad 2-krotnie dłuższy czas pracy na baterii niż modele poprzedniej generacji i 2-krotnie wyższą wydajność w grach niż porównywalne procesory konkurencyjne. Wśród zastosowanych technologii znajduje się szereg nowości z zakresu zarządzania energią, w tym pierwsza implementacja systemu adaptacyjnego skalowania napięcia i częstotliwości (AVFS, tj. Adaptive Voltage and Frequency Scaling) oraz pierwszy wbudowany w procesor dekoder HEVC/H.265. Jest to także pierwszy układ APU, który wykorzystuje techniki kompresji kolorów i systemy obniżające wymagania względem przepustowości. Przedstawiciel firmy AMD w trakcie tej prelekcji omówił też szczegóły dotyczące bramkowania mocy i zegara, nowego, zintegrowanego układu pełniącego funkcję tzw. “mostka południowego” oraz usprawnień na polu trybów uśpienia i spoczynku. Przedstawione zostały także inne nowości, w tym technologia pozwalająca szybko przestawić układ SoC w tryb najniższego poboru energii i samo-odświeżania DRAM.

Podsumowując innowacje AMD, jakie znalazły zastosowanie w 6. generacji procesorów AMD APU Serii A, powstały po to, aby zapewnić energooszczędność wraz ze zwiększonym zagęszczeniem tranzystorów, które produkowane są w dobrze znanym i zoptymalizowanym kosztowo, 28-nanometrowym procesie produkcji.