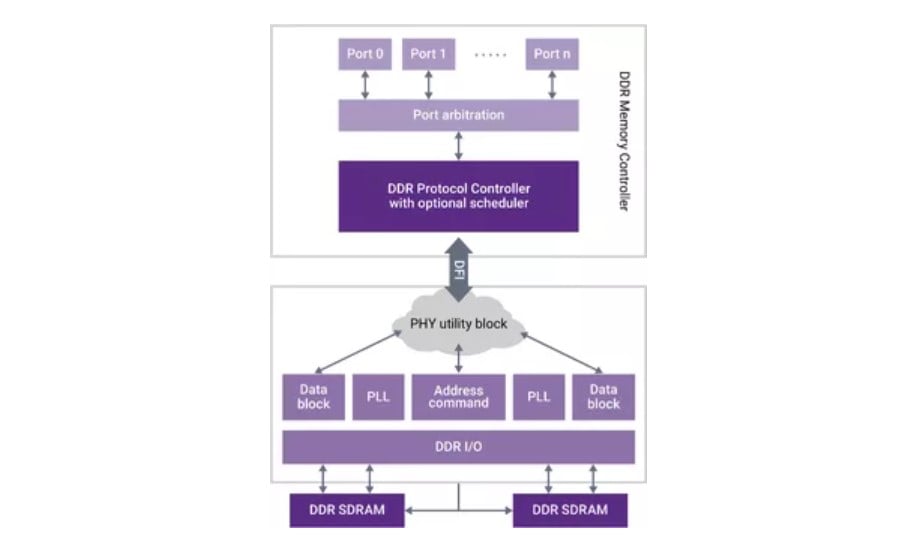

Najnowszy DesignWare IP firmy Synopsys obejmuje kontroler i interfejs PHY dla zastosowań z układami pamięci DDR5 lub DDR4

W rzeczywistości Synopsys jest pierwszą firmą, która rozpoczęła oferowanie fizycznego interfejsu (PHY) DDR5/DDR4 i związanego z pamięciami kontrolera, z myślą m.in. o nowej generacji układów SoC. “Nowej generacji”, bo wykorzystującej m.in. nowe architektury, jak i 5 nm proces technologiczny firmy TSMC. Dzięki tytułowemu interfejsowi, producenci SoC będą mogli dodać oba typy pamięci w swoich układach. W bardziej praktycznym ujęciu cyferek należy wspomnieć o tym, że DesignWare DDR5/DDR4 PHY obsługuje transfer danych z szybkością do 6400 MT/s.

Czytaj też: Poznaliśmy limity mocy mobilnych Intel Alder Lake. Mowa o serii M oraz P

Na szczęście Synopsys ujawniło nie tylko dostępność, ale też szczegóły tego, co przygotowało. Tak też DesignWare IP firmy Synopsys zawiera kontroler DDR5/DDR4 z harmonogramem poleceń, obsługą protokołu pamięci, opcjonalnym wsparciem ECC, obsługą dwukanałowej transmisji i interfejsem DFI 5.0. Po stronie tego, co najważniejsze, jego blok pamięci obsługuje 64 CAM wpisów zarówno dla odczytu, jak i zapisu przy zachowaniu opóźnień na poziomie 8 cykli zegara. Dodatkowo może współpracować nie tylko z firmowym PHY, ale też innymi, obsługującymi DDR5.

Czytaj też: Rekordowa sprzedaż pojemności dyskowej. Sprzedano mniej, ale pojemniejszych HDD

Wedle informacji, kontroler można zaprogramować za pomocą interfejsu Arm AMBA 3.0 APB. Oczywiście zarówno kontroler, jak i PHY obsługują wszystkie standardowe funkcje JEDEC DDR4 i DDR5, a jego wykorzystanie umożliwi producentom ruszenie z produkcją nowych sprzętów na bazie 5 nm układów własnej produkcji.

Czytaj też: Znamy sytuację na rynku układów półprzewodnikowych. Jest źle

Pierwsze co wpada nam do głowy, kiedy myślimy o wykorzystaniu ogłoszonego właśnie DesignWare IP, sprowadza się do wspomnianych układów SoC. Jednak producenci będą mogli wykorzystać go również przy produkcji procesorów centralnych czy kontrolerów SSD, których współpraca z pamięciami dynamicznymi (DRAM) w formie bufora bezpośrednio rzutuje na to, jaką wydajność nośnik będzie oferował. Warto jednocześnie podkreślić, że firma posiada już od dłuższego czasu podobne rozwiązanie związane z LPDDR5, czyli wariantach o niższym poborze energii z myślą o m.in. smartfonach. Znalazły się one m.in. we flagowym Snapdragonie 888 firmy Qualcomm.