Giganci w branży zaczęli współpracować nad standardem łączenia wielu matryc. Co zapewnia standard chipletów UCIe?

W dążeniu do spełnienia prawdy zawartej w Prawie Moore’a, producenci procesorów centralnych skłaniają się w stronę tworzenia nie monolitycznych, a wielomatrycowych układów. Obejmuje to łączenie w ramach jednego układu kilku matryc krzemowych, czyli właśnie krzemowych chipletów. Tym określeniem nazywamy wszystkie krzemowe układy, które w ten sposób łączą się ze sobą.

Czytaj też: Nawet 18432 rdzeni CUDA i ogromne pokłady cache, czyli kolejne informacje o GeForce RTX 4000

Takie podejście uwalnia producentów od problemu zbyt dużych i tym samym zbyt trudnych do stworzenia procesorów. Dzięki niemu z wafla krzemowego można wyprodukować znacznie więcej sprawnych układów i następnie połączyć je, aby spróbować dorównać tradycyjnemu monolitycznemu rdzeniowi pod kątem możliwości.

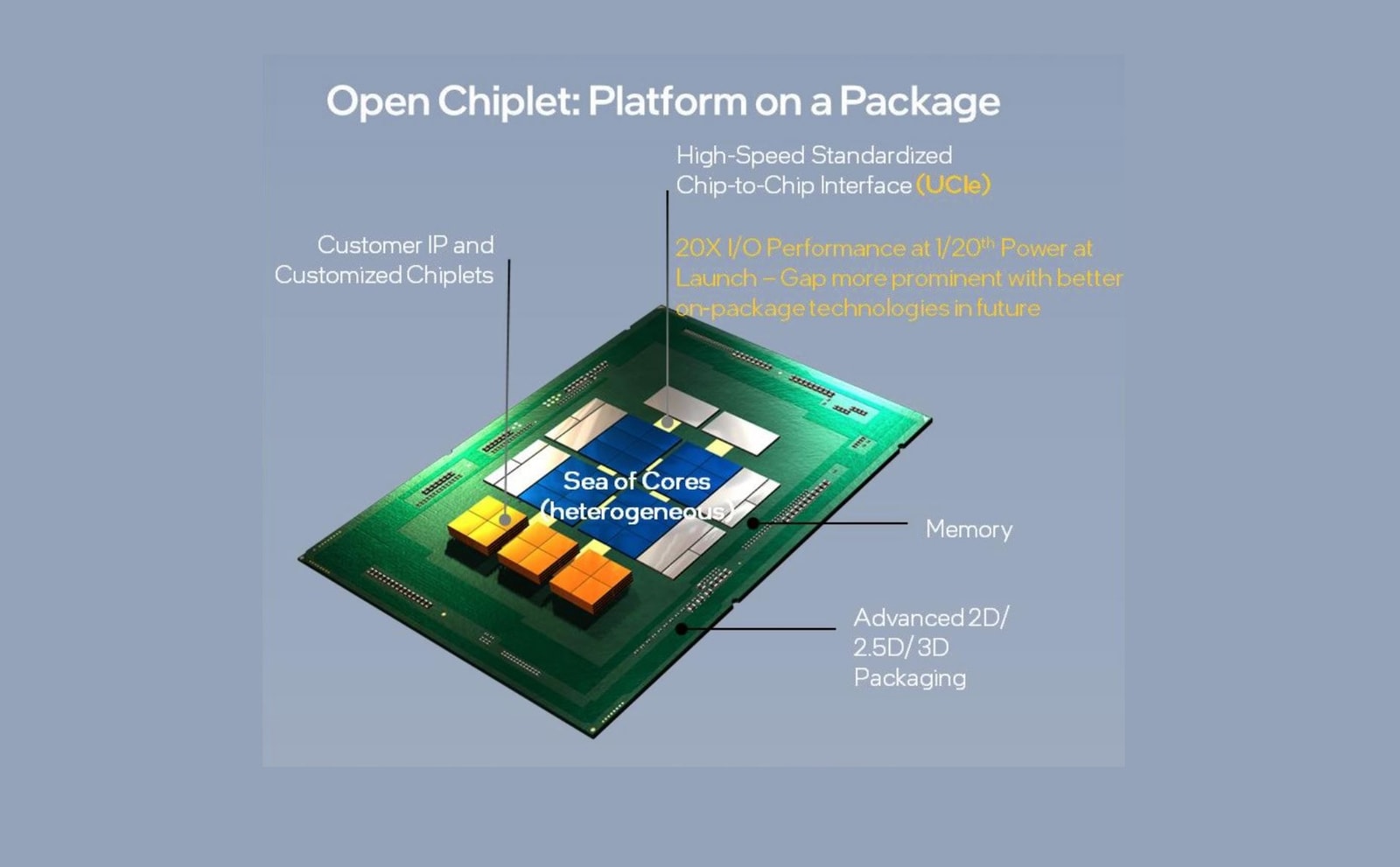

W dobie zyskujących na popularności procesorów MCM (Ryzeny są już nimi od dawna, a Radeony mają zacząć być od serii RX 7000), jak i układów SoC, które przecież integrują w sobie wiele układów, taka inicjatywa może wyjść rynkowi technologii tylko na dobre. UCIe 1.0 powstało bowiem wyłącznie po to, aby zapewnić producentom kompletne i znormalizowane połączenie die-to-die (czytaj: między chipletami) na wszelkich frontach, bo od warstwy fizycznej aż po testy zgodności.

Czytaj też: Kolejne przecieki ujawniają nam coraz więcej informacji o Motoroli moto g22

Jest to kluczowe zwłaszcza dla SoC (System-on-Chip), które często łączą w sobie układy różnych producentów, więc zachowanie kompatybilności między nimi może być wyzwaniem. UCIe będzie dążyło do tego, aby opracować wręcz technologię plug-and-play dla tych chipletów, bo ma na celu maksymalne ustandaryzowanie połączeń międzychipletowych, choć z zapewnieniem wielu opcji dla różnych sektorów i poziomów wydajności.

Czytaj też: Skafander kosmiczny dla każdego. Druk 3D ma uratować astronautów od niedopasowanych kombinezonów

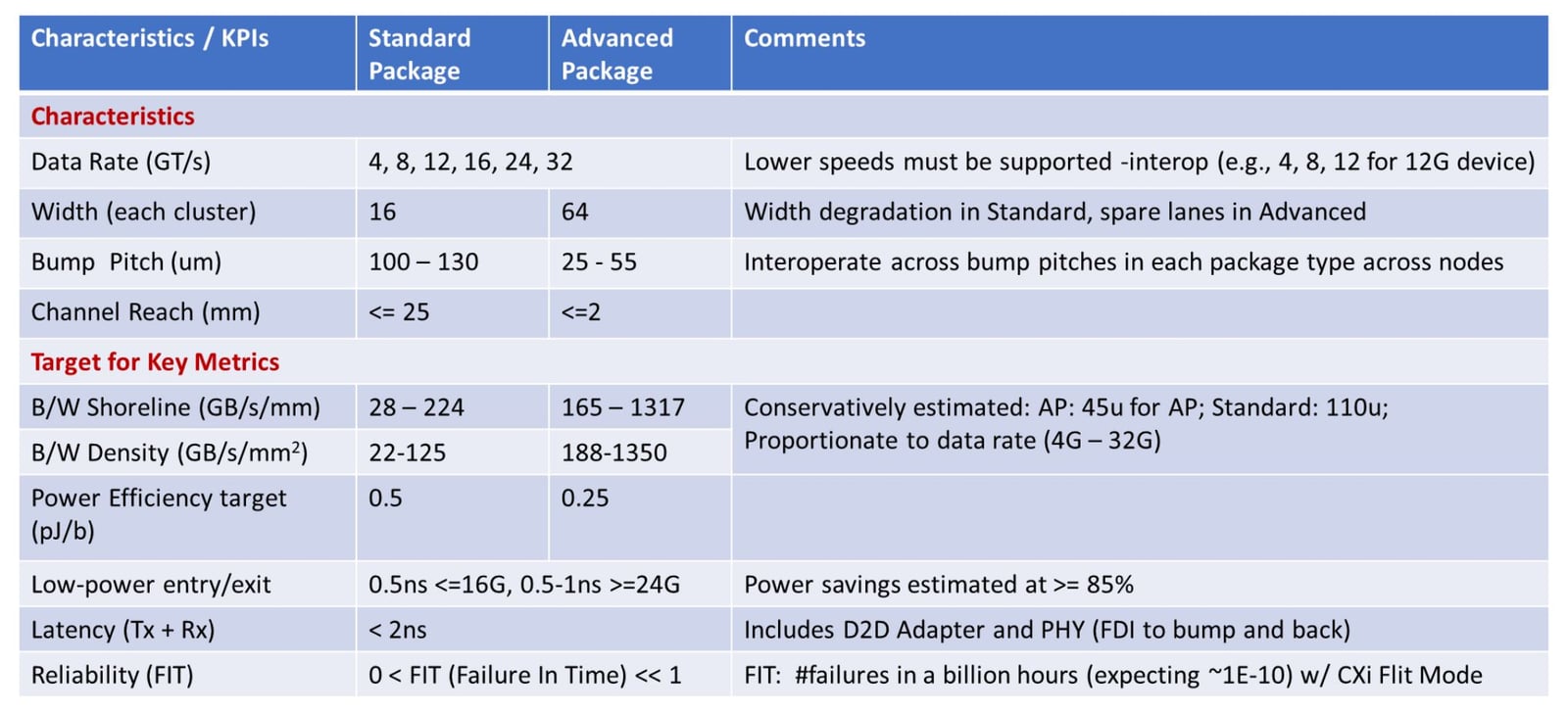

Co ciekawe, UCIe będzie musiało zawalczyć na rynku ze Bunch of Wires od Open Compute Project, ale na papierze wydaje się znacznie bardziej zaawansowane. Przykłady? Lepsza wydajność energetyczna (0,5-0,25 pJ/bit vs 0,5-0,7 pJ/bit), wyższe prędkości (32 vs 16 GT/s), znacznie okazalszy parametr Shoreline Bandwidth (3,8 Tb/s vs 1,28 Tb/s) i nawet zastosowania, bo UCIe zamiast ograniczać się do pakietów MCP, obsługuje również większość opcji opakowań 2D i 2,5D.