Cadence osiągnęła kamień milowy rozwoju podstaw dla PCIe 5.0. Produkcja PHY i kontrolera ruszyła, a zestawy projektowe są na wyciągnięcie ręki

Przechodzenie na następną generację sprzętów to nie tylko opracowanie nowego procesora centralnego, graficznego czy pamięci operacyjnej. To też zadbanie o interfejs czy kontroler, który umożliwi ich wspólną pracę. Właśnie nad tego typu sprzętem pracowała firma Cadence Design Systems specjalnie z myślą o PCIe 5.0 i niedawno pochwaliła się sukcesem swojej współpracy z TSMC.

Czytaj też: Cena niereferencyjnej karty graficznej Arc A380 nasuwa jedno pytanie – czy ktoś oszalał?

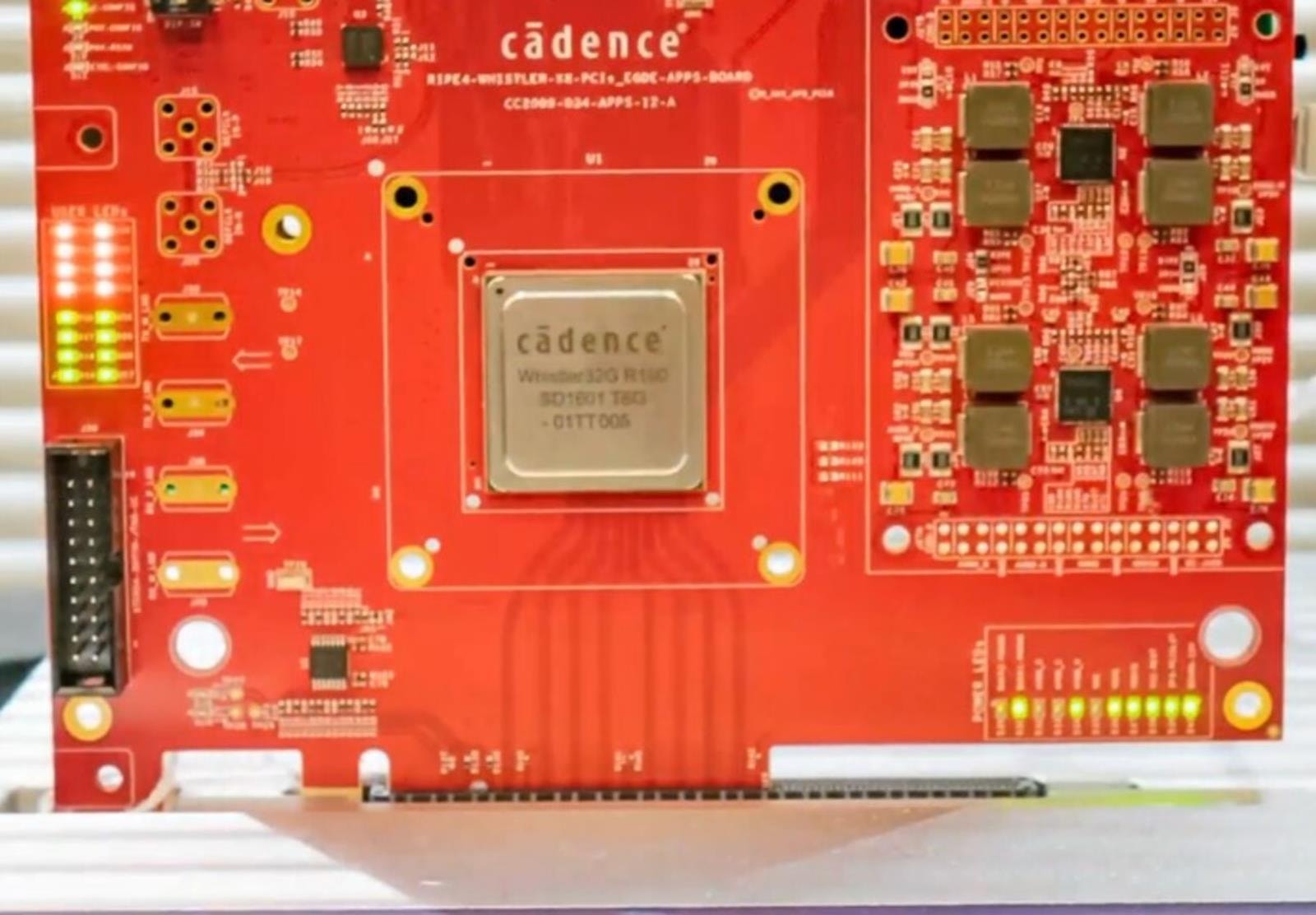

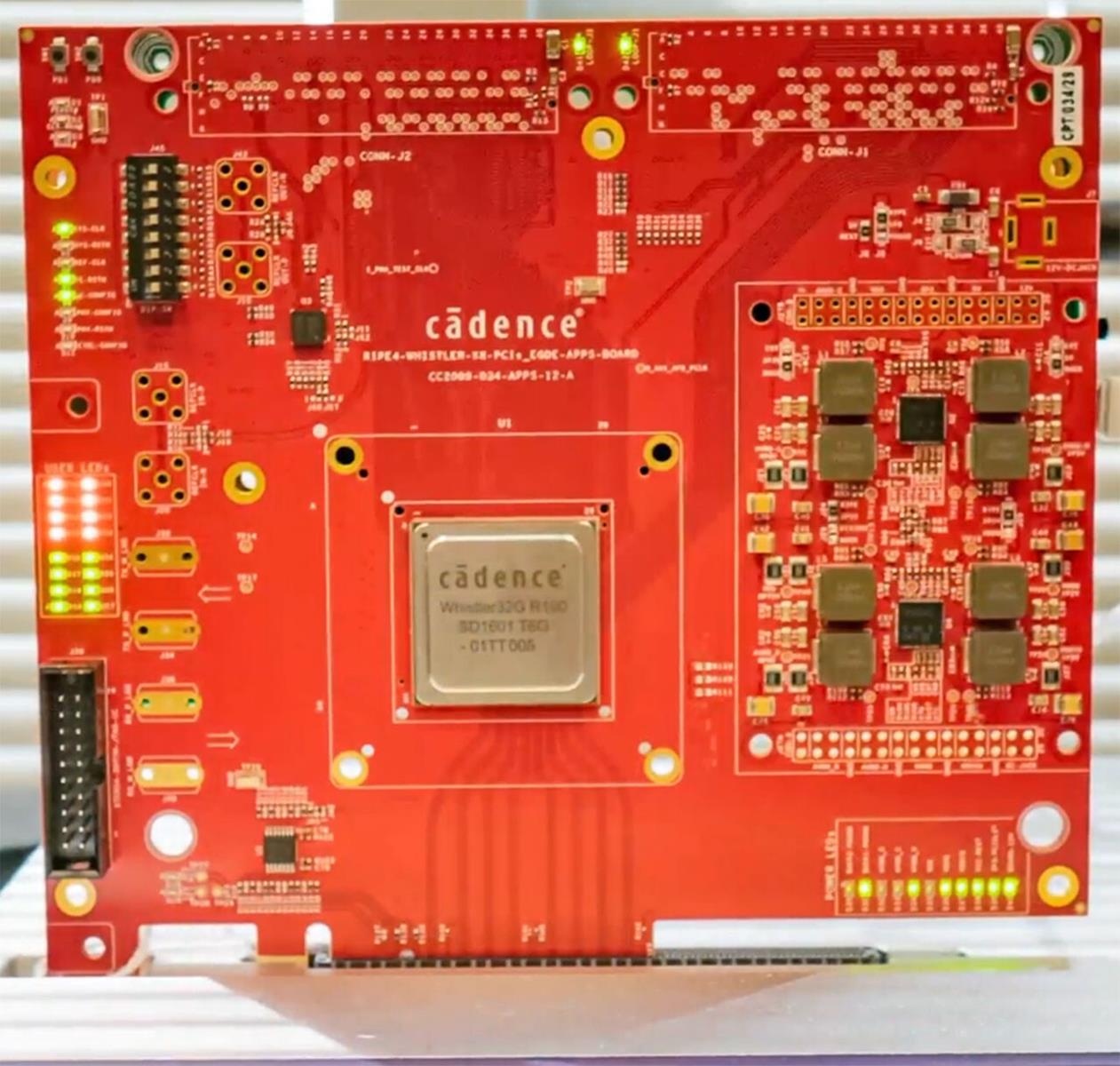

W ogłoszeniu Cadence Design Systems przeczytamy, że jej PHY i Controller IP (kolejno fizycznego interfejsu (PHY) i kontrolera) dla specyfikacji PCI Express 5.0 (PCIe 5.0) wyprodukowane w technologiach TSMC N7, N6 i N5 przeszły pomyślnie testy certyfikacyjne PCI-SIG podczas pierwszej w branży konferencji dotyczącej zgodności ze specyfikacją PCIe 5.0.

Czytaj też: Play rusza z „hurtownią” światłowodu FiberForce. Kolejny duży gracz na rynku

Rozwiązania Cadence zostały przetestowane pod kątem ich pełnego potencjału i spełniły wymagania pełnej prędkości 32GT/s dla technologii PCIe 5.0. Sam test w formie wielu procedur testowych miał za zadanie zapewnić pewność producentom co to tego, czy ich interfejsy PCIe 5.0 w projektach typu system-on-chip (SoC) będą działać zgodnie z oczekiwaniami.

To właśnie z myślą o producentach SoC firma opracowała swoje rozwiązania, które pozwolą projektować niezwykle energooszczędne SoC, jednocześnie przyspieszając czas wprowadzenia produktu na rynek. Nie będzie to zresztą tak odległe, bo zestawy projektowe PCIe 5.0 dla technologii procesowych N7, N6 i N5 firmy TSMC są dostępne do licencjonowania i dostawy już teraz.