Na tle konkurencji ze strony AMD, a nawet Apple, procesory Alder Lake są dla Intela ważne. Ich sukces albo porażka bezpośrednio nakreśli kolejne lata na rynku CPU

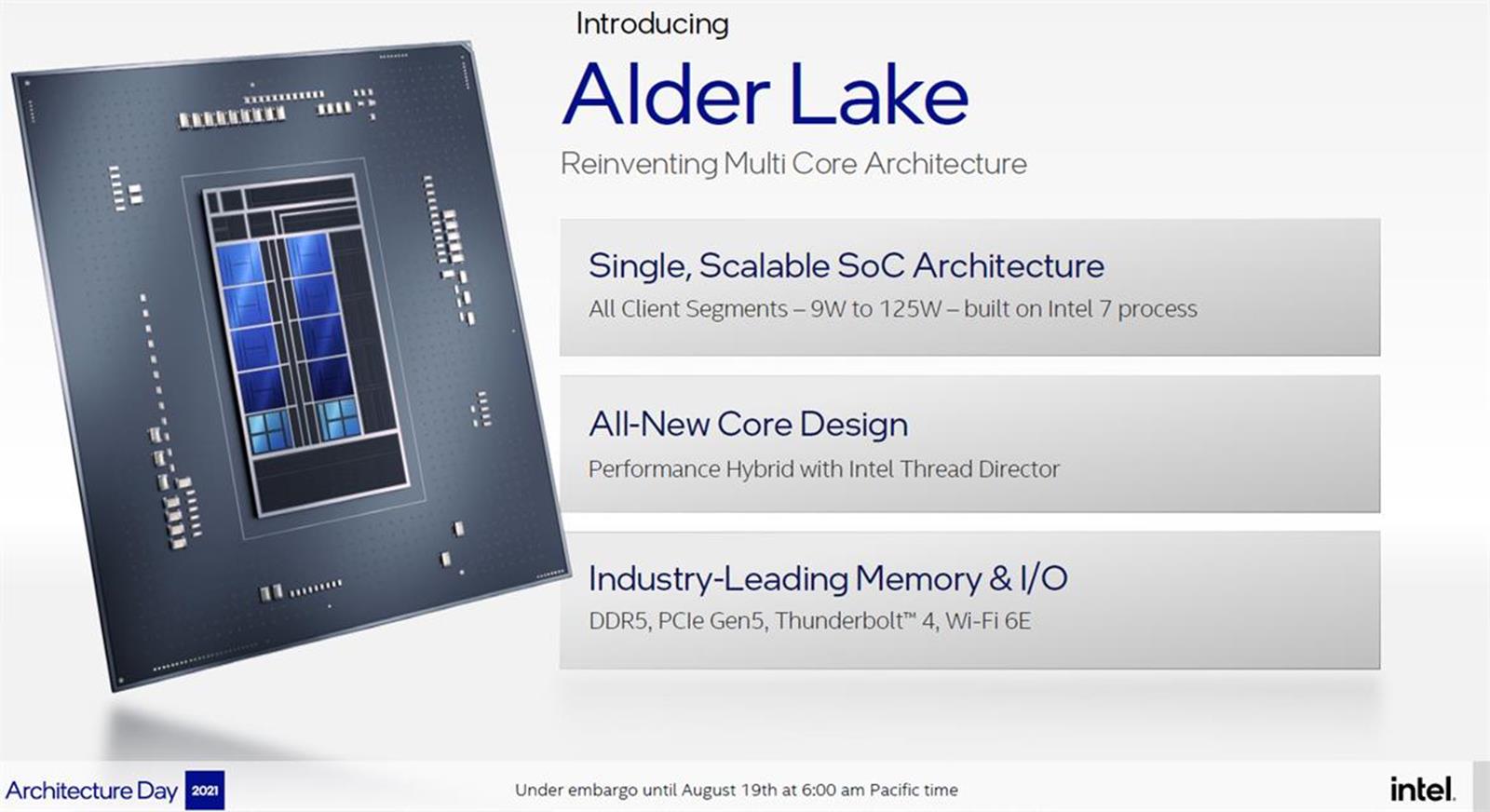

Rodzina procesorów Alder Lake jest dla Intela kluczowa. Może jej sukces nie określi “być albo nie być” firmy, ale z pewnością odbije się na następnych latach działalności Intela na rynku. Zwłaszcza teraz, kiedy AMD rozwija procesory Ryzen w najlepsze, a Apple swoimi M1 udowodniło, że nie potrzebuje sprzętu Intela. Ogromne zmiany struktury i zupełnie inne podejście do projektowania procesorów x86, to wielkie ryzyko, ale wygląda na to, że Intel ma plan i jasną wizję, która może i zapewne pociągnie za sobą również konkurencję.

Czytaj też: Wydajność Ryzen 9 5980HX ujawniona. Jak wypada na tle Intel Core i9-11980HK?

Na papierze procesory Alder Lake wygląda świetnie. Z jednej strony wreszcie dogoniły ofertę AMD pod kątem liczby rdzeni, a z drugiej jako pierwsze wprowadzają obsługę nowego standardu interfejsu (PCIe 5.0) i pamięci operacyjnej (DDR5). Zapowiadają się więc tak, jakby kupno flagowych układów z tej rodziny CPU było równoznaczne z sięgnięciem po procesor na długie lata. Poniekąd, bo skutecznie przeszkodził temu brak wsparcia obliczeń z wykorzystaniem instrukcji AVX-512 w układach konsumenckich, które wprawdzie nadal są praktycznie nieobecne na konsumenckim rynku, ale to zapewne kwestia czasu, aż ulegnie to zmianie.

Zaplecze technologiczne Intel Alder Lake

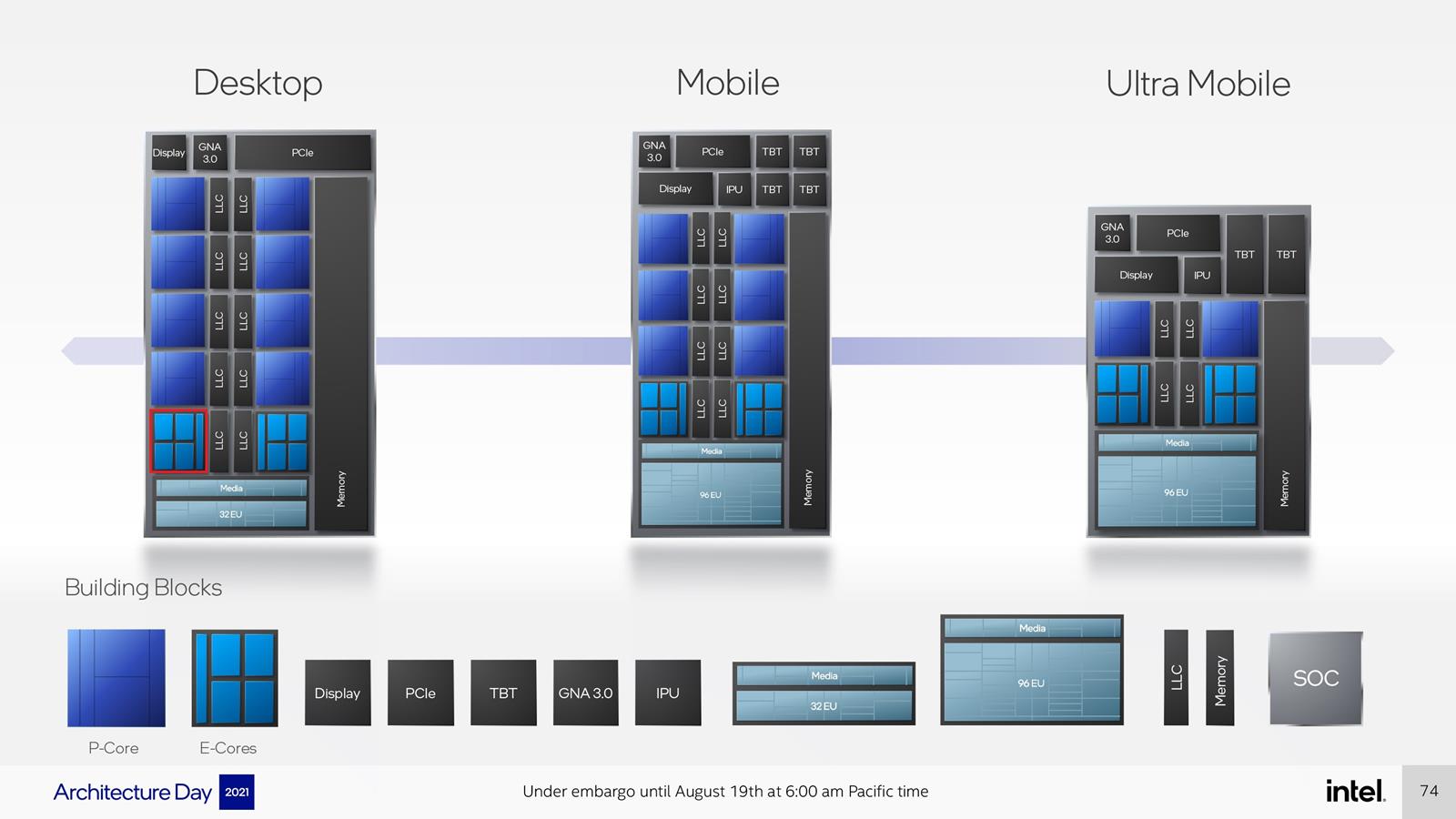

Finalnie procesory Alder Lake doczekają się trzech wariantów pomyślanych z myślą o urządzeniach stacjonarnych i mobilnych o TDP wahającym się od 9 do 125 watów. Te pierwsze będą najbardziej zaawansowane pod kątem procesora centralnego (CPU), ale te przeznaczone na rynek mobilny będą z kolei posiadały bardziej rozbudowany rdzeń graficzny (32 vs 96 jednostek wykonawczych “EU”) na bazie architektury Xe LP (12. generacji) wyprodukowany w ramach procesu Intel 7, czyli dawniej 10 nm Enhanced SuperFin.

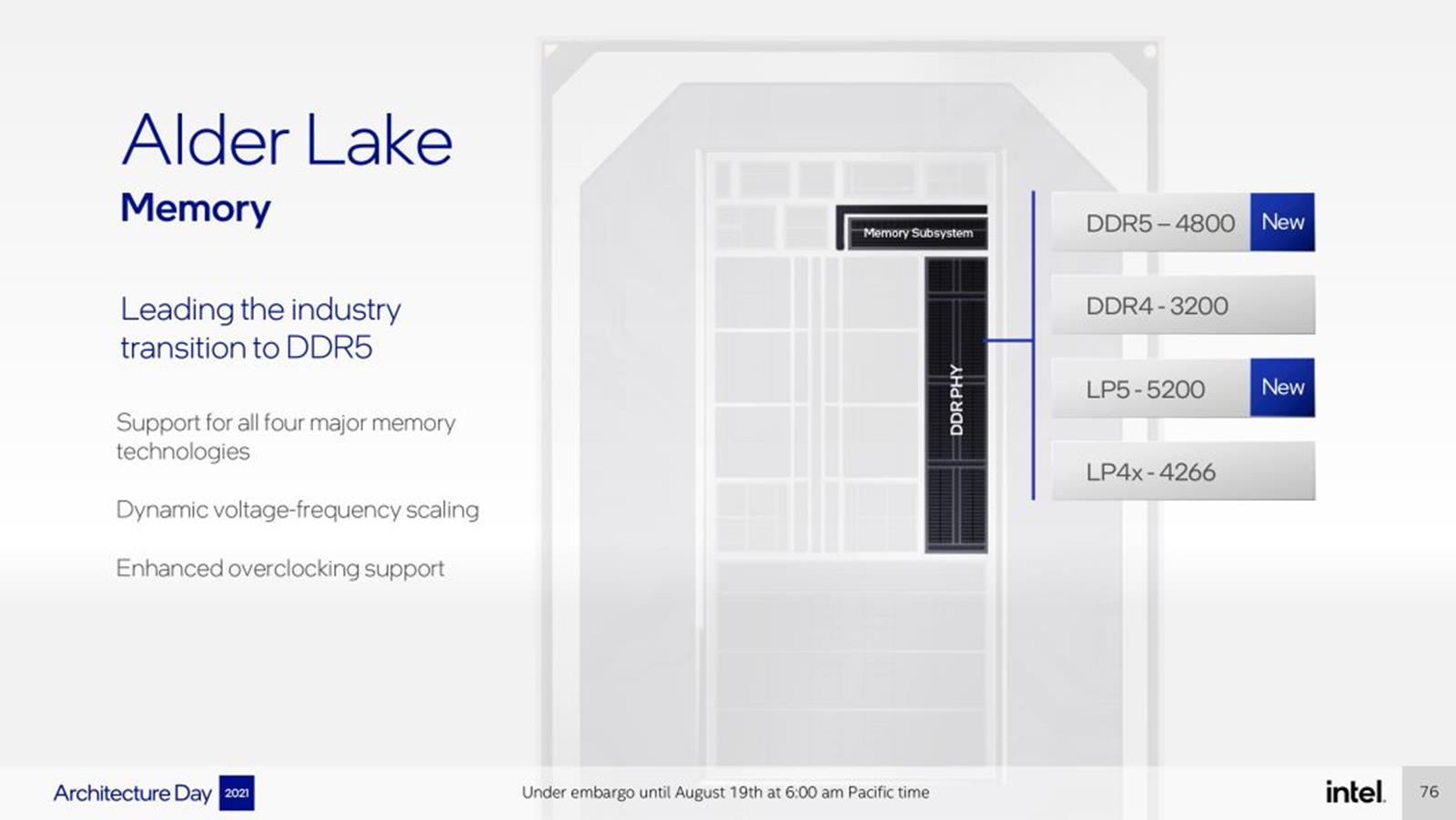

Po stronie kontrolerów pamięci operacyjnej w grę wejdą nie tradycyjne dwa, a aż cztery standardy. Alder Lake obsłużą bowiem DDR5-4800 i LPDDR5-5200, a także DDR4-3200 i LPDDR4x-4266, ale nie oznacza to, że każda z płyt głównych będzie np. wspierać nowy standard, bo te najpewniej będą zarezerwowane dla topowych płyt głównych, czy urządzeń mobilnych.

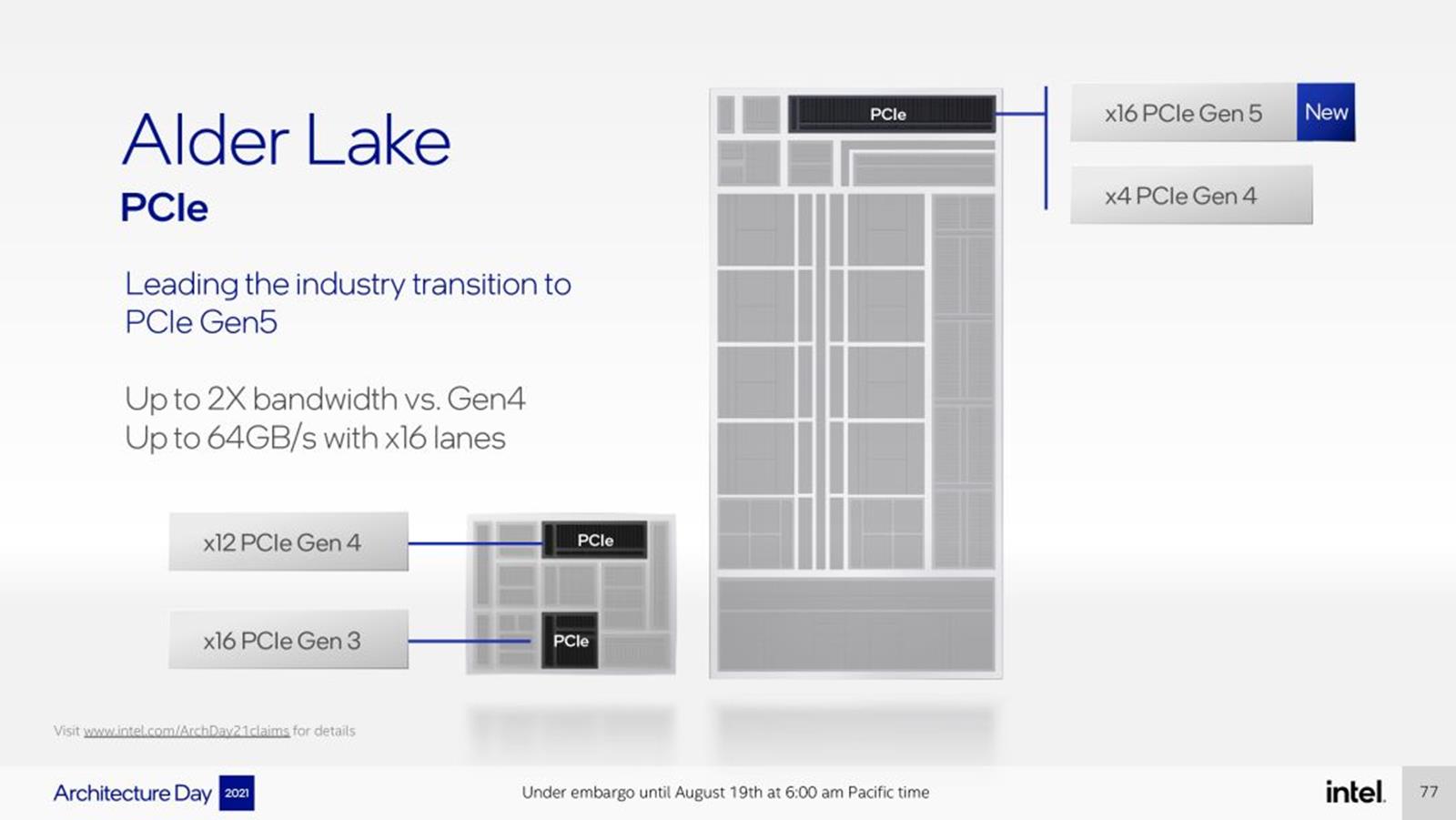

Jeśli o interfejs idzie, Alder Lake jako pierwszy obsłuży na rynku konsumenckim standard PCIe 5.0, oferujący przepustowość 64 GB/s przy szesnastu liniach, czyli tych przeznaczonych dla kart graficznych. Intel wspomniał też o dodatkowym PCIe 4×4, ale na ten moment nie wiadomo, czy będziemy mogli go wykorzystać, czy posłuży jako interfejs między procesorem a chipsetem. Z kolei mobilne układy będą oferować 12 linii PCIe 4.0 i 16 PCIe 3.0, jak również łączność Wi-Fi 6E oraz Thunderbolt 4.

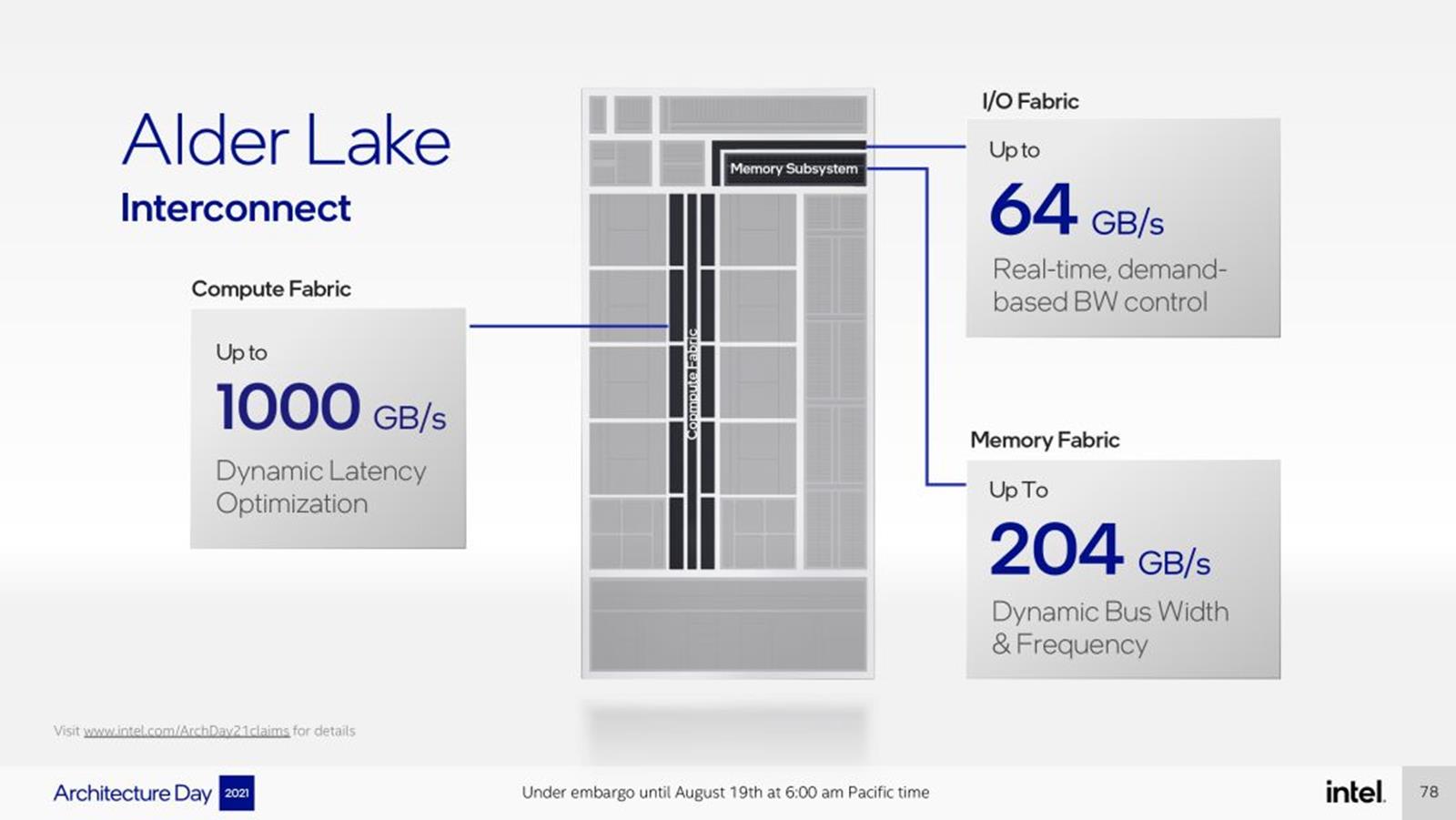

Z łączeniem poszczególnych podsystemów Intel miał zresztą sporo do zrobienia, bo należało połączyć ze sobą dwa rodzaje rdzeni, pamięć podręczną i wydajne kontrolery. Tę funkcję realizuje nowy rodzaj magistrali w formie sieci o przepustowości 1000 GB/s dostępnej dla wszystkich elementów, który dynamicznie dostosowuje się do wszystkich połączeń. Podobnie działa sama struktura pamięci z dostępem do magistrali o przepustowości do 204 GB/s, której szerokość i częstotliwość pracy można łatwo regulować w odpowiedzi na konkretne obciążenia.

Rdzenie Intel Alder Lake

Przechodząc do tego, co najważniejsze, czyli heterogenicznej struktury rdzeni Alder Lake, warto przypomnieć, że te podejście zostało zaczerpnięte z pomysłu ARM w postaci big.LITTLE stosowanego od dawna na rynku mobilnym. Wszystko rozbija się o połączenie w jednym procesorze dwóch rodzajów rdzeni – tych wydajnych, które nie zważają na zużycie energii oraz tych energooszczędnych, których najważniejszą rolą jest utrzymanie najlepszego stosunku wydajności do wykorzystywanych watów.

Intel określa je kolejno mianem Performance Core i Efficiency Core, które bazują odpowiednio na architekturze Golden Cove i Gracemont. W Alder Lake to po prostu rozwinięcie znanej z Lakefield technologii Intel Hybrid, której zaawansowanie wzniesiono na zupełnie nowy poziom, ale o tym dopiero za chwilę. Różnice między tymi rdzeniami są ogromne i to już w fizycznym ujęciu, bo każdy rdzeń P jest osobnym bytem, a rdzenie E “po cztery” są upakowane w jednym miejscu.

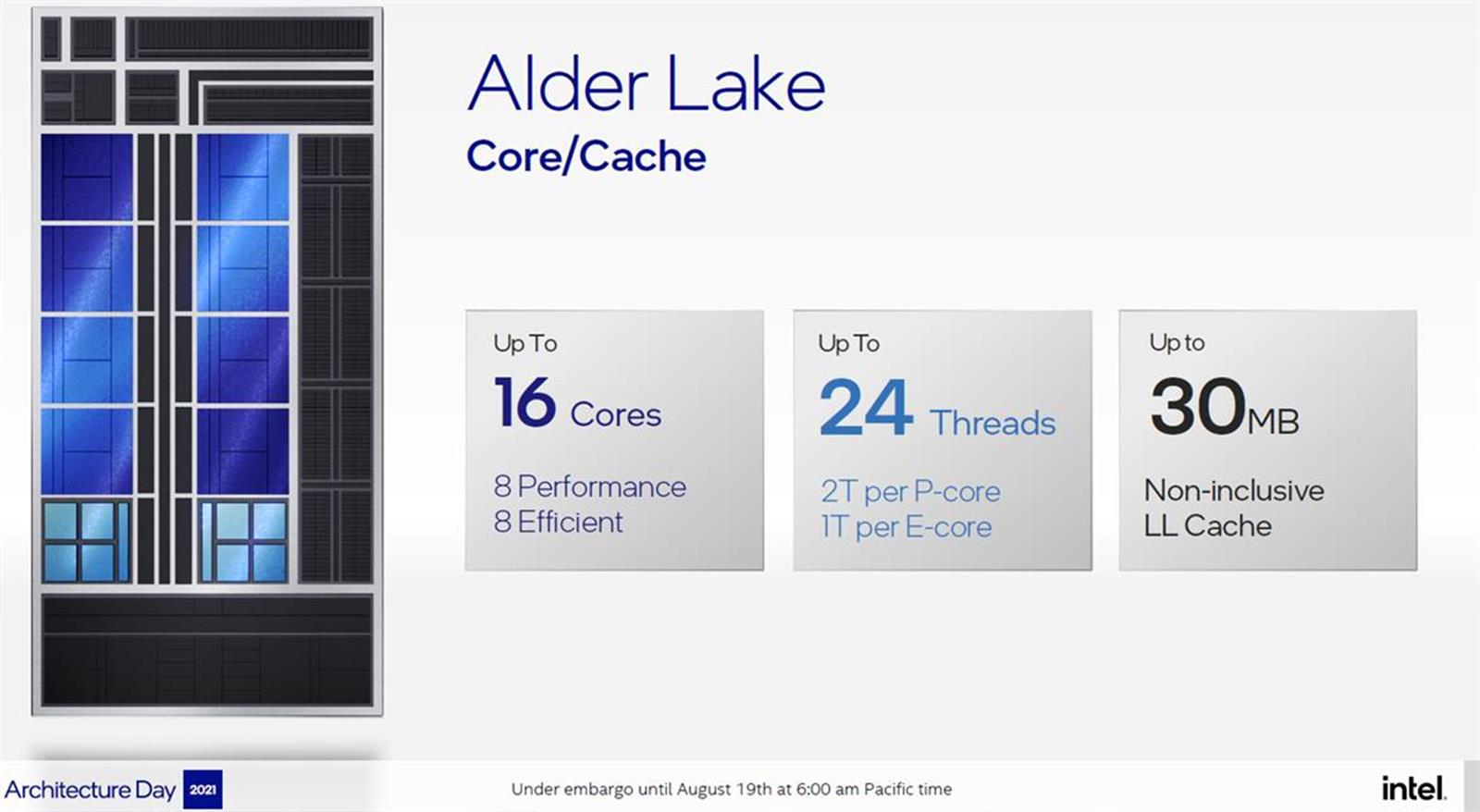

Zanim przejdziemy do szczegółów, warto wiedzieć, że flagowymi procesorami Alder Lake będą te z 16 rdzeniami (8 rdzeniami P ze wsparciem wielowątkowości, czyli technologii HyperThreading oraz 8 rdzeniami E) i 24 wątkami. Będą one korzystać z dynamicznie przydzielanego zapasu 30 MB pamięci L3, czyli podręcznej trzeciego poziomu. Te poziomu pierwszego i drugiego będą już ekskluzywne dla każdego rdzenia.

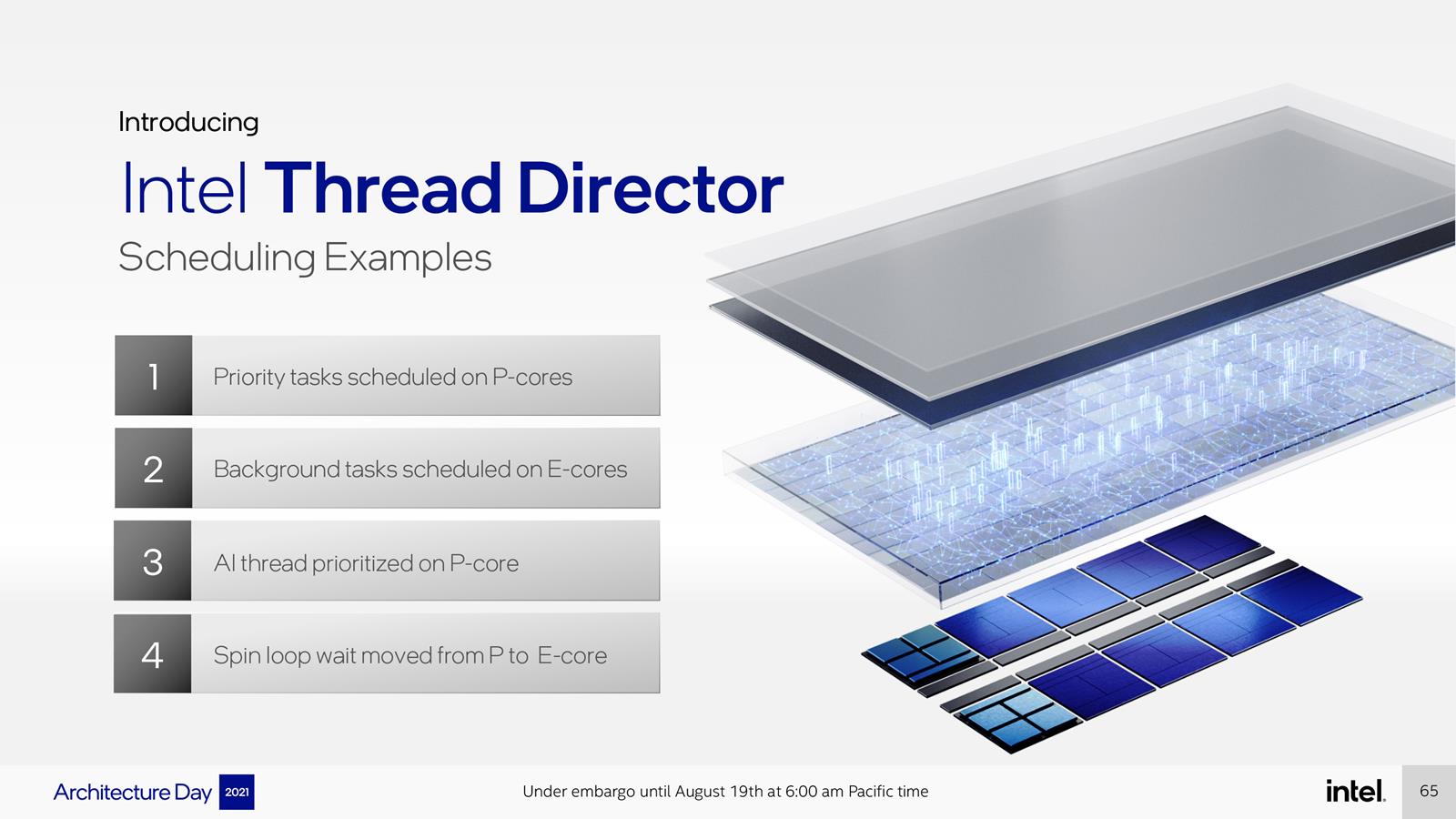

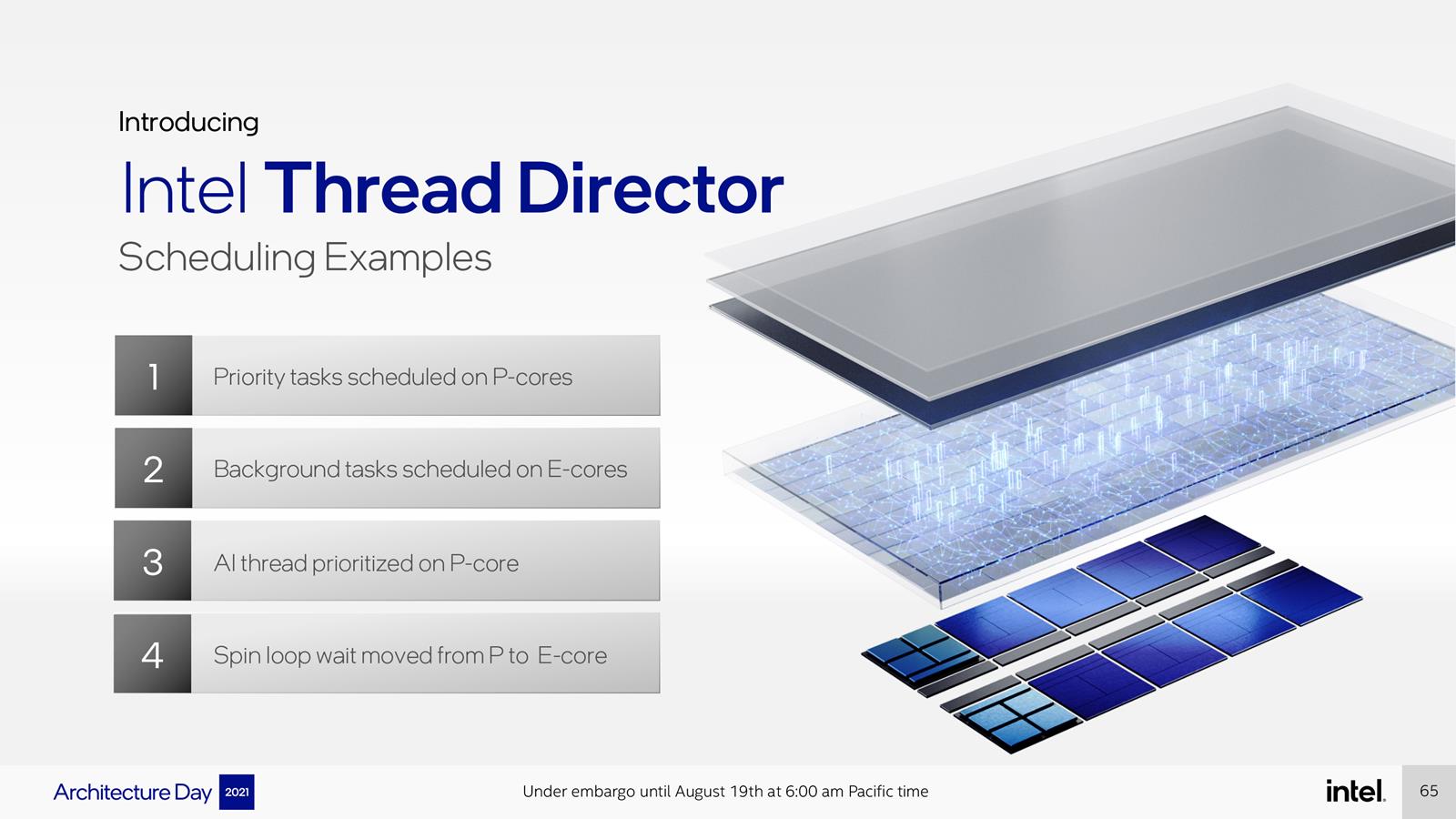

Thread Director, bo obciążeniem trzeba jakoś zarządzać

Gdyby strona hardware była jedyną, o którą musiałyby martwić się firmy, to świat byłby dla nich za piękny. Przykład tego widzieliśmy przy premierze Intel Lakefield, pierwszych procesorów, które posiadały dwa różne rdzenie i których potencjał nie był wykorzystywany przez sposób, w jaki systemy operacyjne, przyzwyczajone do pojedynczego rodzaju rdzeni, oddelegowały do nich zadania.

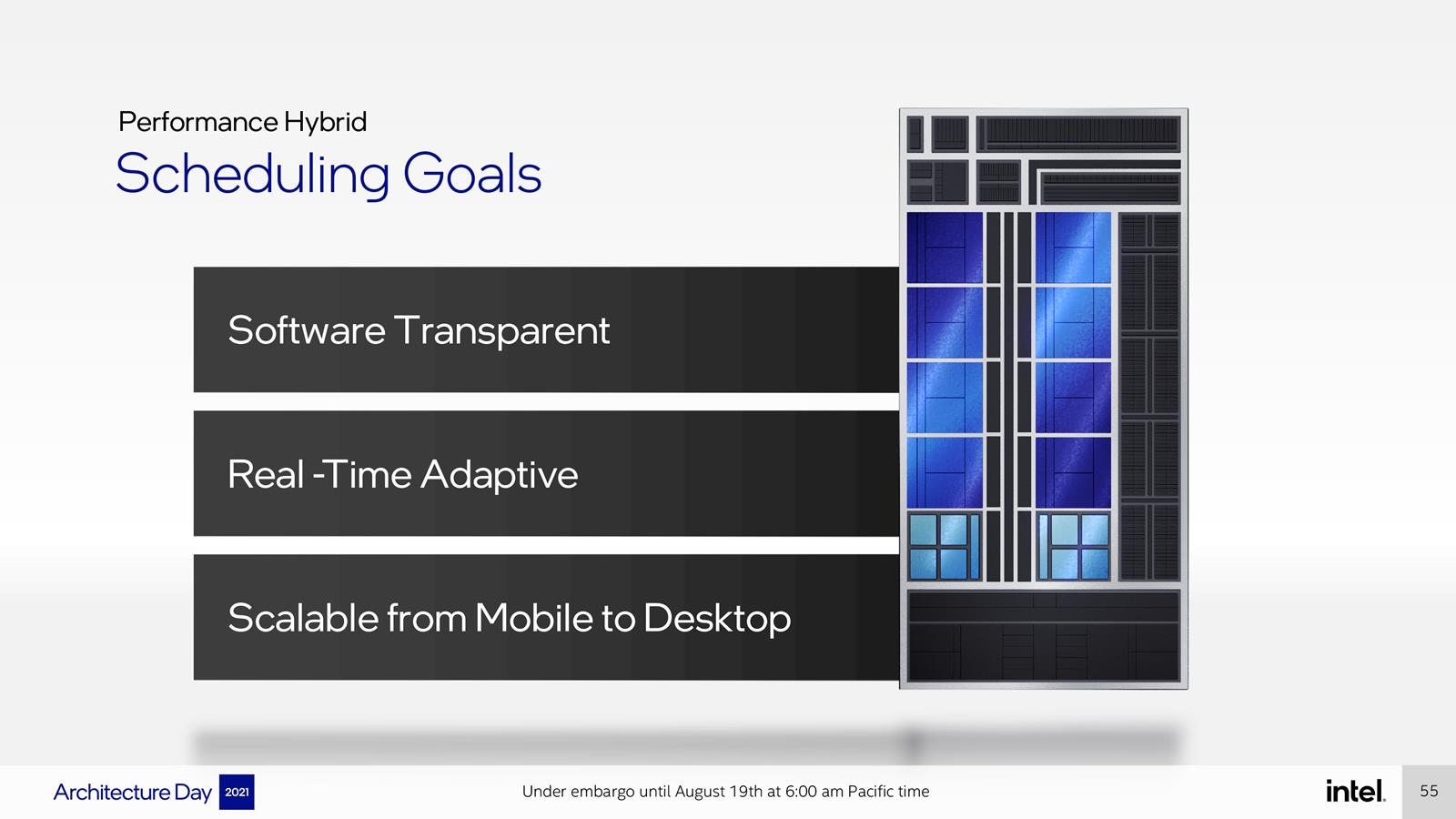

To jednak zmieni technologia Thread Director firmy Intel, która sprowadza się do sprzętowych elementów w procesorze pozwalających systemowi operacyjnemu i procesorowi pracować w tandemie. Te są bowiem w stanie zapewnić systemowi Windows 11 szereg danych telemetrycznych niskiego poziomu. Te dane system wykorzystuje po to, aby w inteligentny i zoptymalizowany sposób przekierowywać konkretne wątki do rdzeni P lub E.

Podsystem zbiera informacje na temat mocy, temperatury czy nawet rodzaju zadania, które system rzuca procesorowi, a dzięki temu, że ten jest dynamiczny i elastyczny, jego decyzje mogą różnić w zależności od kombinacji warunków i obciążeń w danym momencie. Thread Director umożliwia nawet przerzucanie wątków między rodzajem rdzeni zależnie od ich fazy. System operacyjny Windows 10 nie ma dostępu do tego typu danych i zamiast tego bazuje na prostym schemacie obciążenia i priorytetu, dlatego procesory Intel Alder Lake nie rozwiną skrzydeł na innych systemach, których shedulery są tak prymitywne.

Nie będzie to jednak nieprzejrzyste, bo w ramach interfejsu API PowerThrottling programiści będą w stanie wpływać na to, jak konkretne wątki będą traktowane przez procesor. Warto podkreślić, że tym najważniejszym fizycznym elementem w procesorach Alder Lake, służącym technologii Thread Director, jest nowy mikrokontroler zarządzania energią w każdym rdzeniu, który zbiera podobne dane w czasie nie mili-, a mikrosekund.

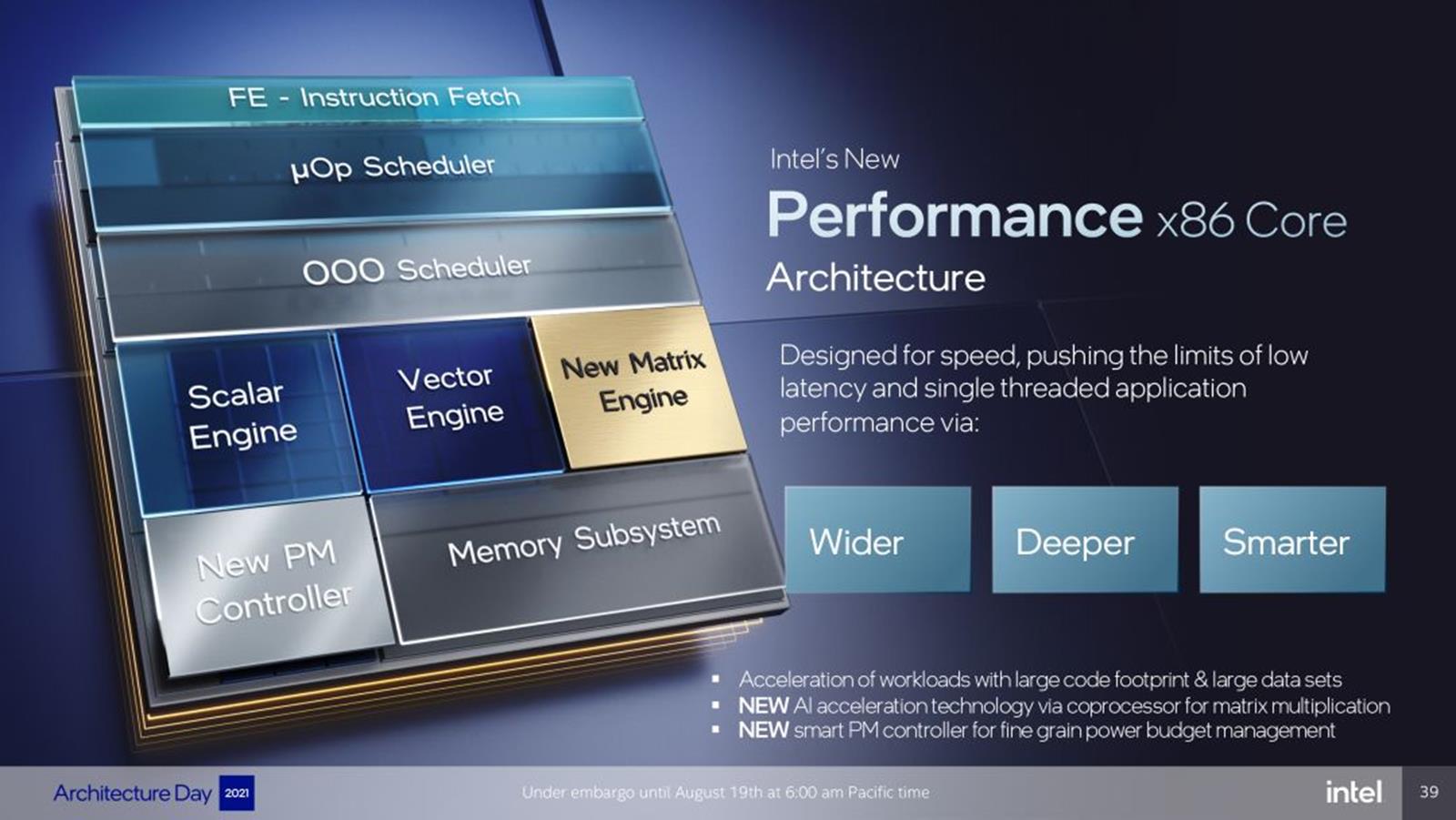

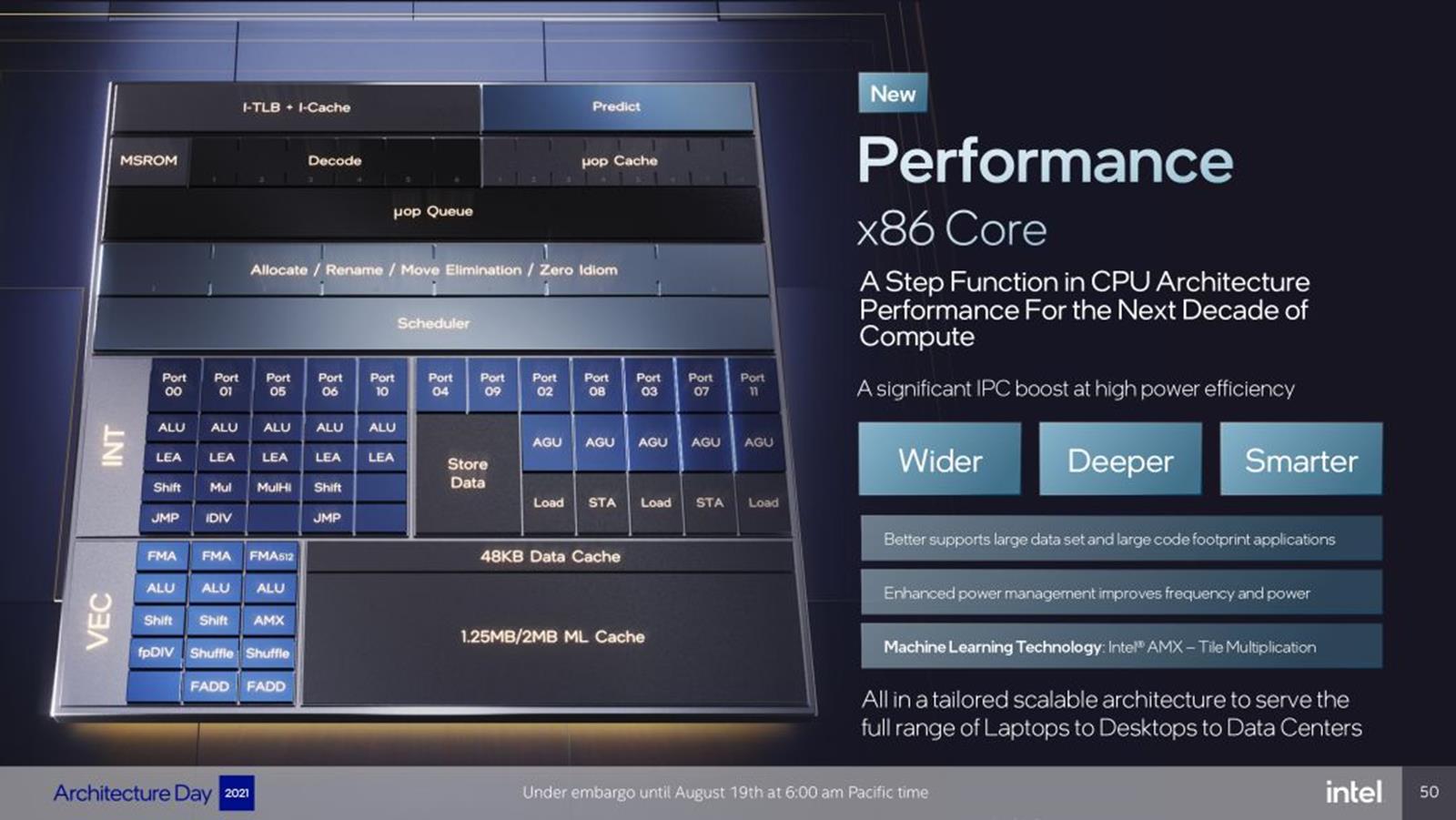

Rdzenie P, czyli Performance Core na bazie architektury Golden Cove

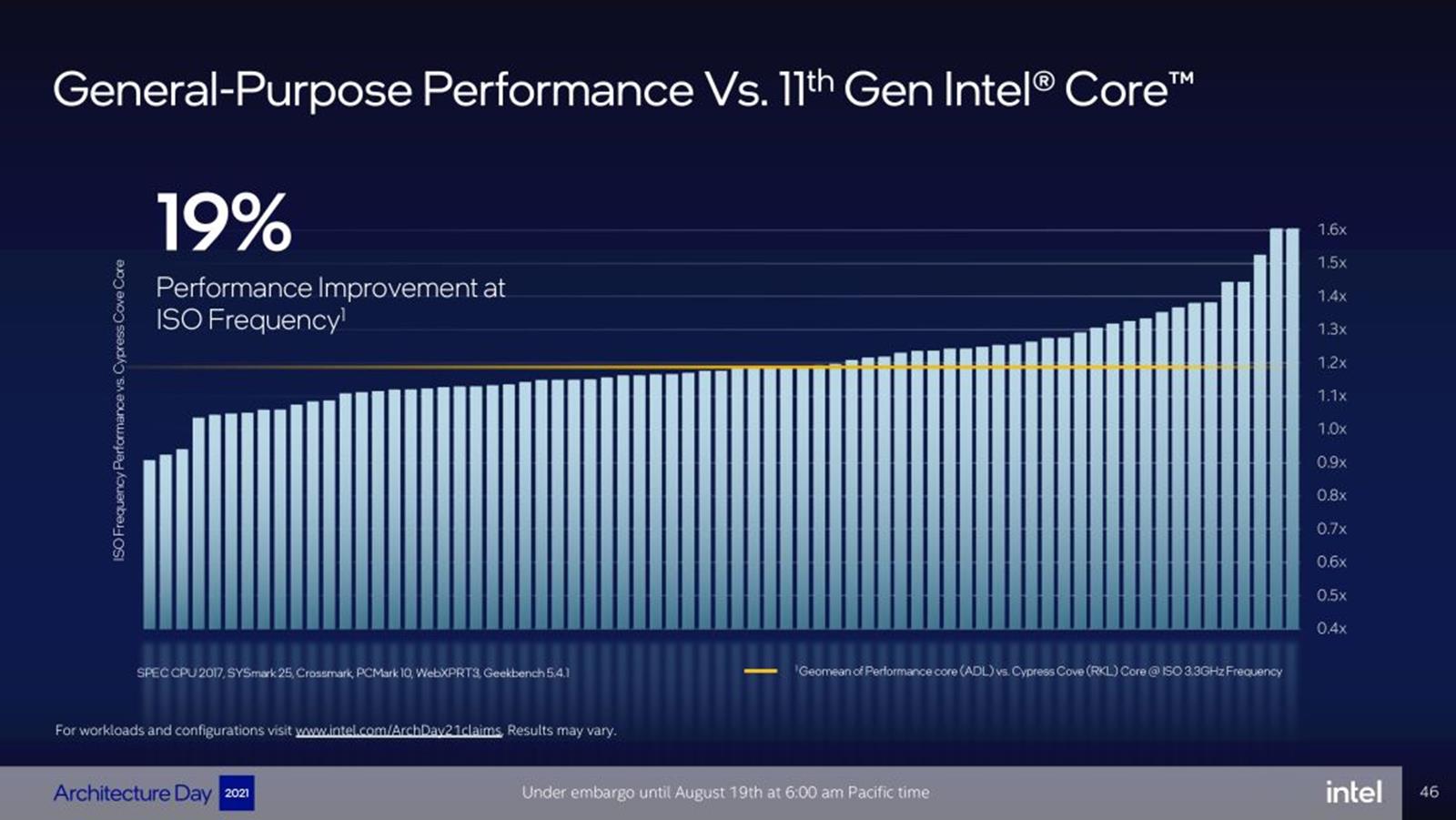

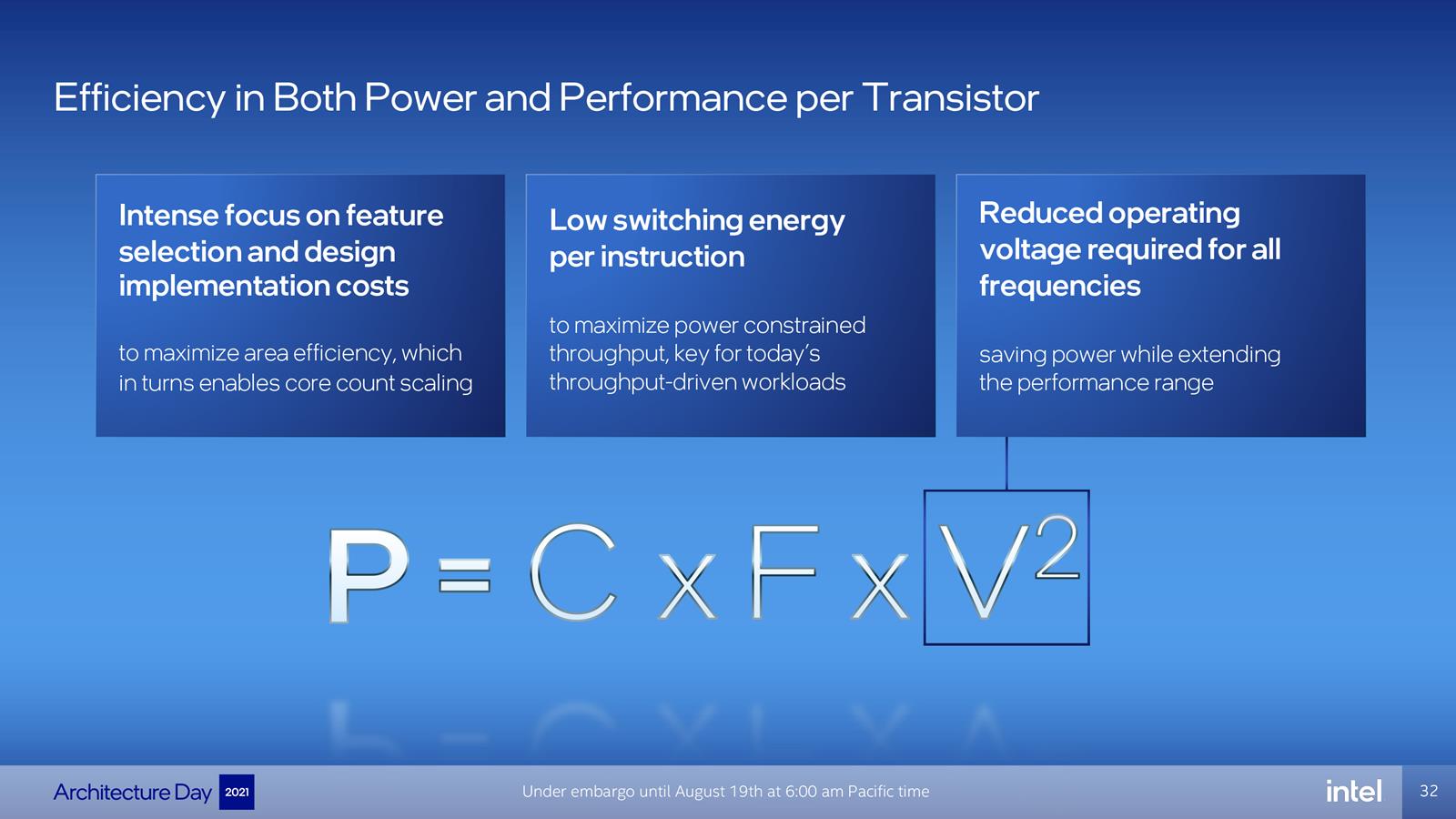

Planem Intela, w przypadku P Core na bazie architektury Golden Cove, było opracowanie najwydajniejszego w historii firmy rdzenia… i to się udało, co potwierdza 19-procentowy wzrost wydajności w porównaniu z rdzeniami obecnymi w 12. generacji Intel Core przy tej samej częstotliwości. Oczywiście, o ile uwierzymy firmie, ale na ten moment nie pozostaje nam nic innego. Zwłaszcza że może być tylko lepiej po przejściu na wyższe częstotliwości, dzięki procesowi Intel 7. Intel dokonał tego poprzez ulepszenia na praktycznie każdym froncie.

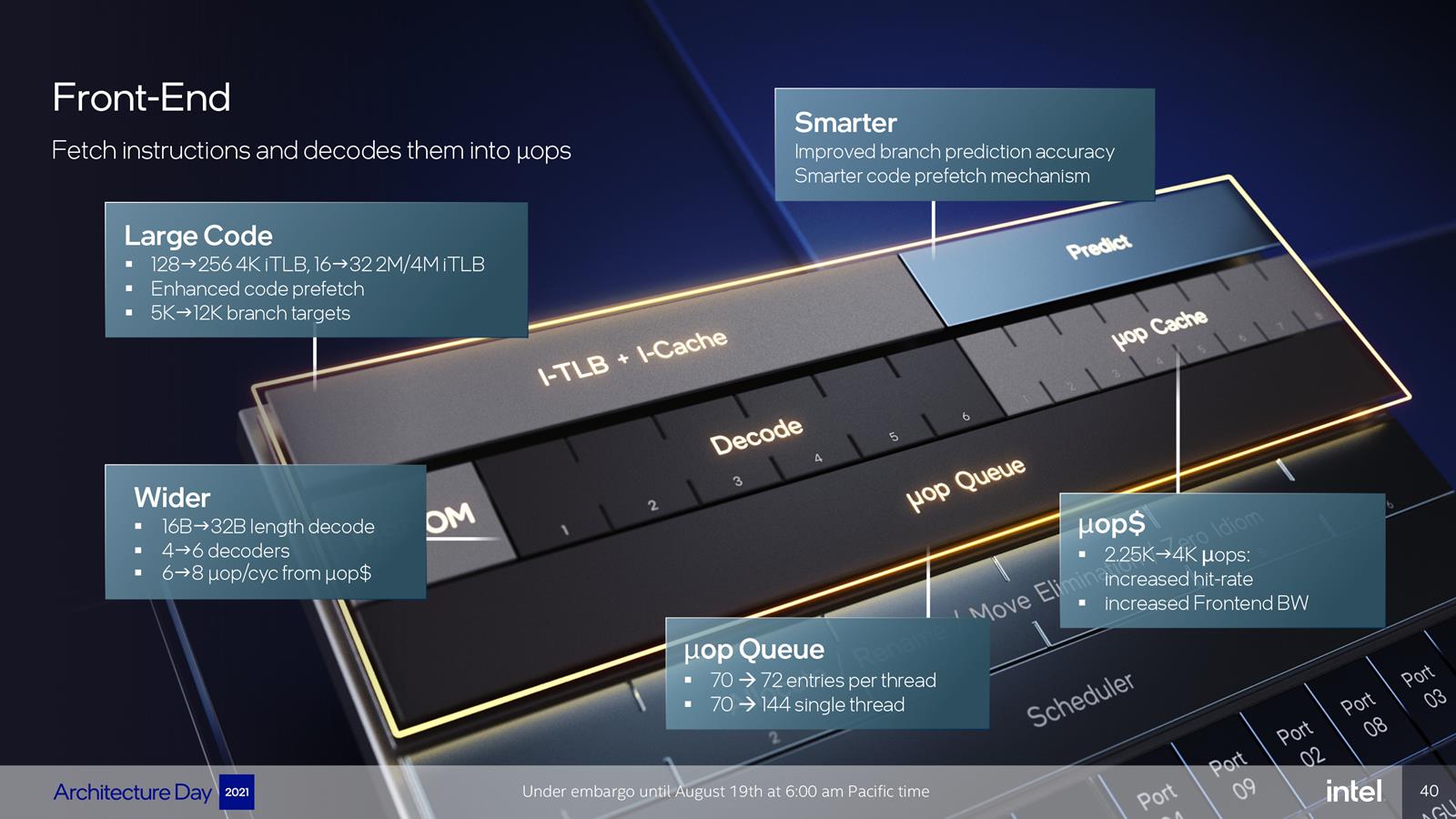

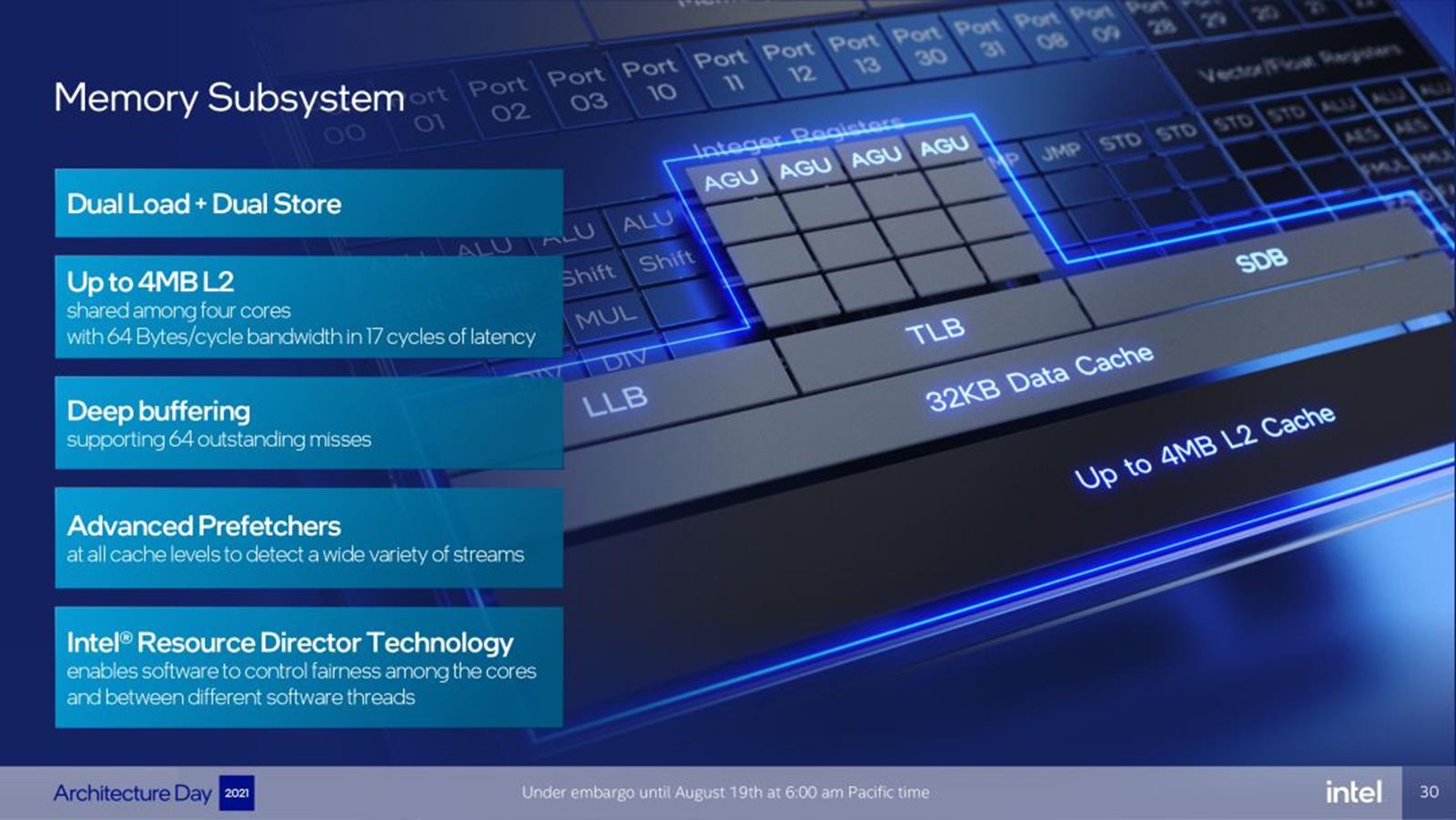

Zaczynając od pamięci podręcznej, ta pozostała na poziomie 48 KB dla L1, ale wzrosła w przypadku pamięci drugiego poziomu z 512 KB do 1,25 MB w przypadku tych konsumenckich (1,25 vs 2 MB w przypadku profesjonalnych). To jednak tylko wierzchołek góry lodowej, bo Intel zwiększył liczbę portów z 2 do 3, zwiększając ich bufory ładowania i przechowywania, a nawet preselektory, operujące teraz na czterech, a nie dwóch stronach (pages). Pamięć podręczna obsługuje z kolei teraz nie 6, a 8 mikrooperacji na cykl i na raz może przechować 4000, a nie 2250 z nich.

Intel poprawił również zasilanie mikrooperacyjne zarówno z dekodera, jak i pamięci podręcznej, zwiększając długość dekodowania z 16 do 32B na cykl i dodając dwa dodatkowe dekodery. Z kolei podsystem Branch Target Buffer, służący jako pamięć podręczna dla prefetchera, doczekał się ponad dwukrotnego wzrostu i algorytmu uczenia maszynowego, który pozwala mu zwiększać lub zmniejszać pojemność w zależności od użytkowania, a tym samym dostrajać moc i wydajność.

Czytaj też: Kontroler HBM3 od Rambus już gotowy. Nawet 1075 TB/s przepustowości

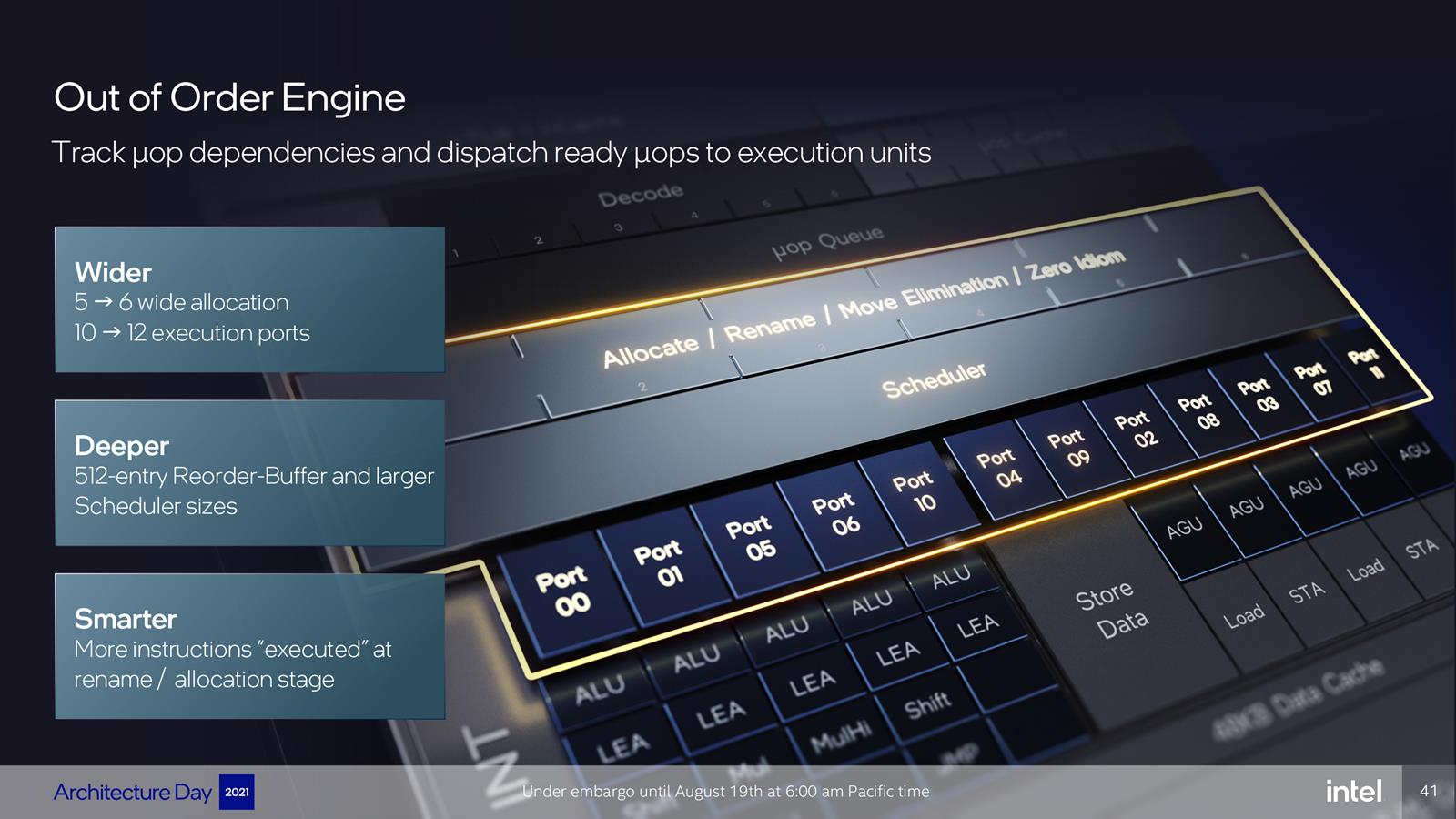

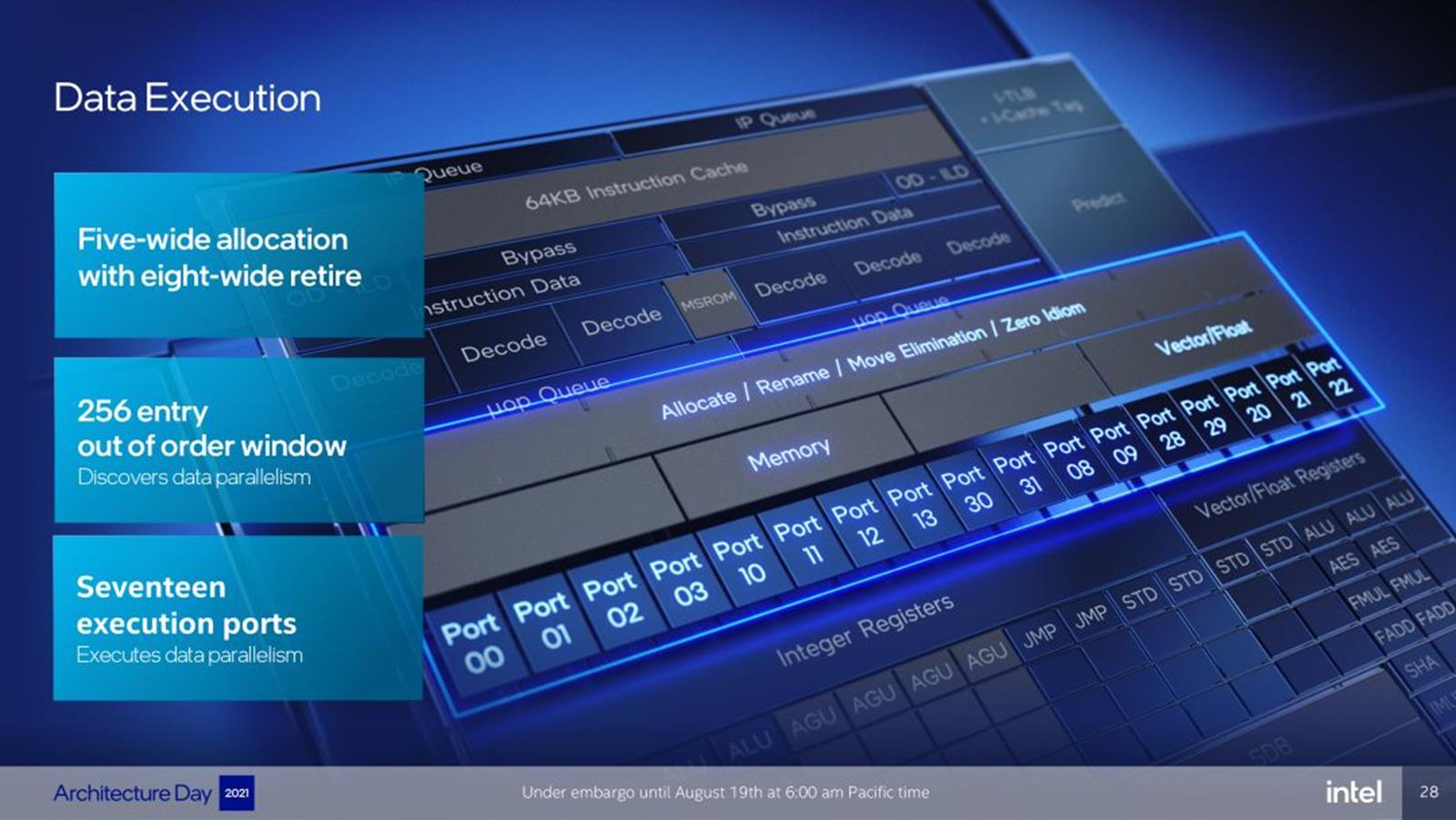

Jednostki alokacji silnika Out of Order (OoO) doczekały się z kolei poszerzenia z 5 do 6 jednostek, a on sam porzucił 352-wejściowy bufor na rzecz 512-wejściowego, mogąc operować na większej liczbie rejestrów fizycznych. Natomiast zarządzający nim harmonogram posiada teraz nie 10, a 12 portów wykonawczych. Całość dopełnia dodatek piątego portu ogólnego przeznaczenia do wykonywania obliczeń z udziałem liczb całkowitych.

Rdzenie E, czyli Efficiency Core na bazie architektury Gracemont

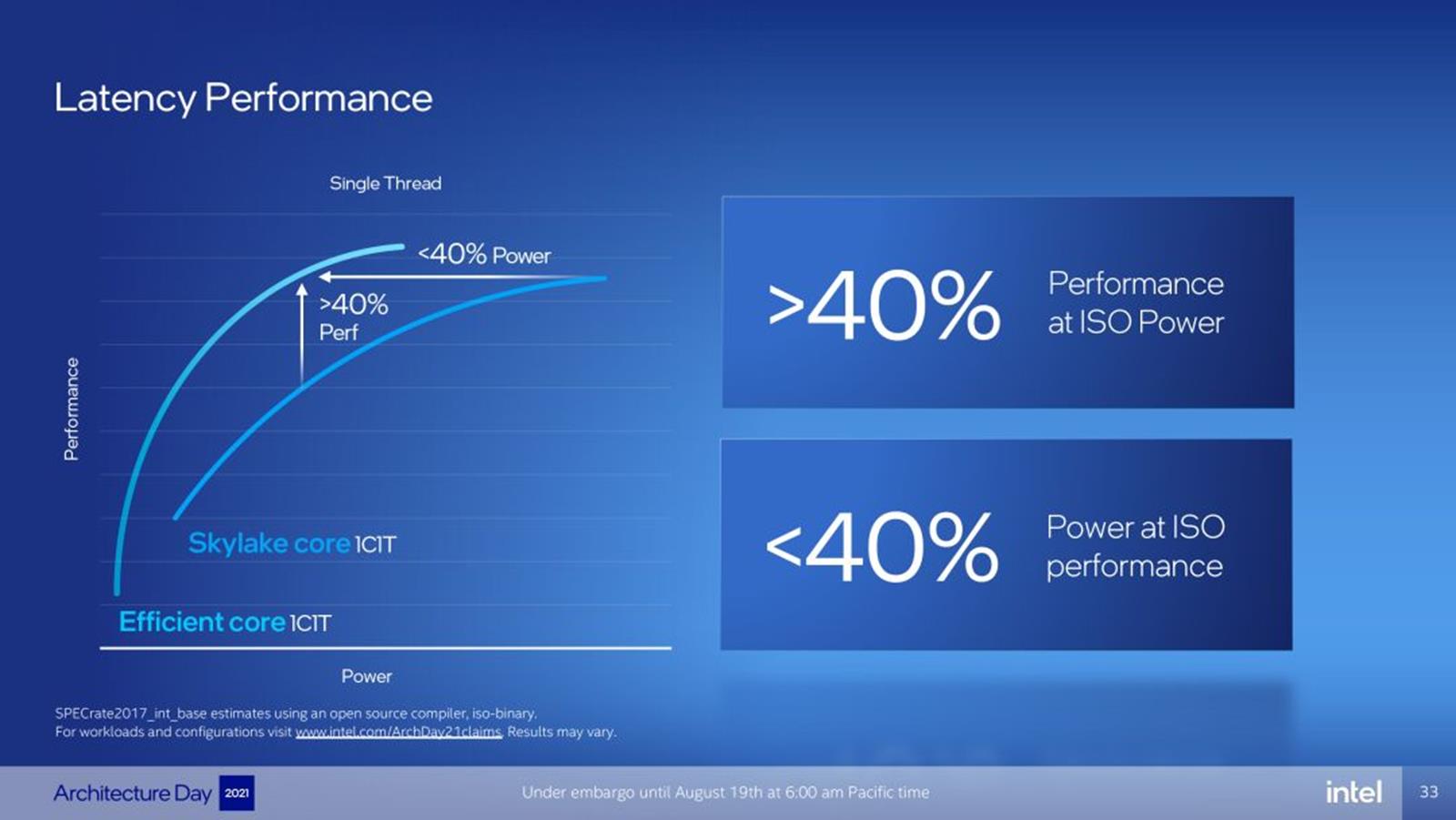

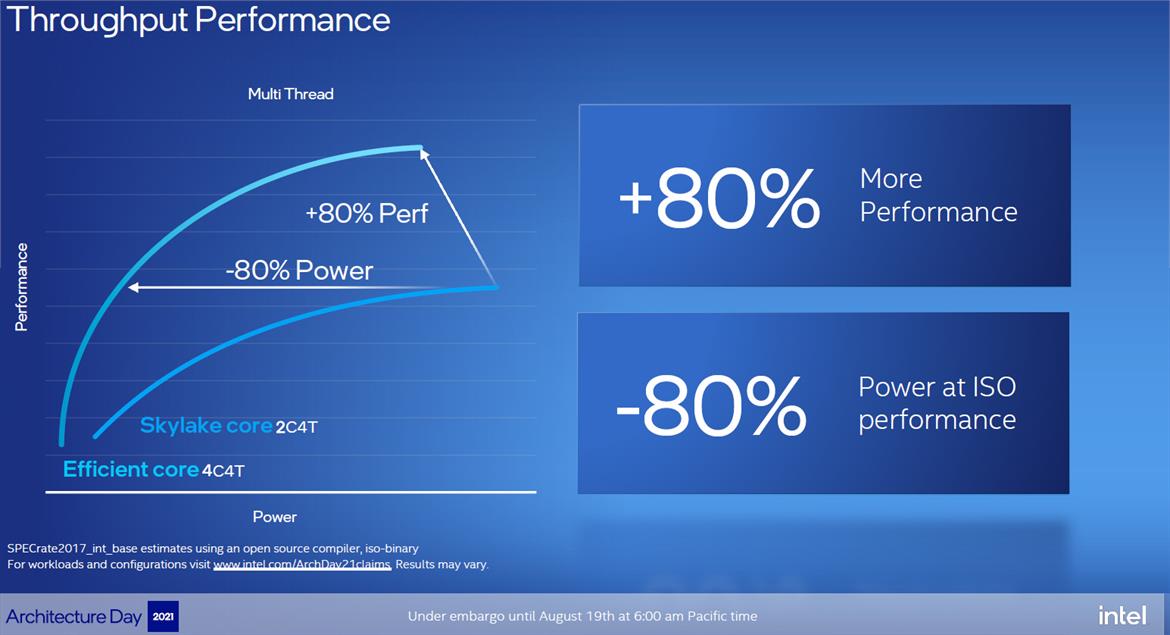

Nazywana dawniej mianem Atom Gracemont, architektura Gracemont służy Intelowi jako podstawa do zapewnienia procesorom Alder Lake rdzeni o rekordowej wydajności pod kątem jej stosunku do pożeranej energii. To również udało się firmie, co reprezentuje wynik jednordzeniowego testu SPECrate2017_int_base, operujący na liczbach całkowitych w porównaniu do wyniku nieznanego procesora Skylake z wyłączoną wielowątkowością.

Jak widzicie powyżej, rdzeń E ‘Gracemont’ zapewnił ponad 40% wydajności przy zużyciu tej samej mocy względem starszego rdzenia. Innymi słowy, rdzeń procesora Skylake pożerał o 2,5 razy więcej energii, aby zapewnić ten sam poziom wydajności. Z kolei poniżej Intel pokazał wydajność w teście przepustowości, gdzie postawiono ze sobą 4-rdzenie Gracemont i dwa rdzenie Skylake, ale z włączoną wielowątkowością. Wynik? O 80% większa przepustowość przy tym samym poborze mocy, albo ta sama przy 80% mniejszym zużyciu energii.

Porównanie ma nas oczywiście przekonać co do wyższości E Core w Alder Lake, ale wynik jest tutaj ewidentnie nieco zmanipulowany. Nie tylko przez fakt, że wielowątkowość dla dwóch rdzeni Skylake zapewnia im wzrost wydajności o jakieś 20-30%, a nie ~100%, jak to ma miejsce przy zwiększeniu liczby rdzeni, ale też przez to, że Skylake jest po prostu znacznie starszym układem.

Przechodząc do szczegółów, E Core ‘Gracemont’ obsługuje instrukcje wektorowe, czy związane z SI, takie jak VNNI i AVX-256, ale o AVX-512 możemy pomarzyć. Intel przy jego projekcie dążył do zmaksymalizowania zakresu częstotliwości oraz najwyższej wydajności przy najmniejszym rozmiarze, dzięki czemu może upychać całą masę tych czterordzeniowych klastrów rdzeni na małym fizycznym obszarze rdzeni, uzyskując wysoką wydajność wielordzeniową.

Jeśli idzie o szczegóły struktury samych rdzeni, Intel zwiększył dokładność przewidywania, dzięki pamięci podręcznej, mogącej przechowywać 5000 instrukcji, które koryguje nowy system przewidywania, generujący dokładniejsze wskaźniki instrukcji. Te przechowuje w 64 KB układach, oszczędzając w ten sposób energię na ich transferze z głównej pamięci podręcznej. Związany z tym pierwszy taki dekoder długości instrukcji Intela na żądanie, generuje informacje przed dekodowaniem, co zapewnia historię poprzednich instrukcji, dzięki czemu znane już kody omijają dekoder w celu zaoszczędzenia energii.

Sam dekoder jest w stanie dekodować do sześciu instrukcji na cykl, łącząc podwójne trzy dekodery, co ponoć zachowuje wydajność energetyczną węższej konstrukcji. Po stronie obliczeniowej znalazły się cztery porty wykonywania liczb całkowitych ogólnego przeznaczenia z podwójnymi mnożnikami i dzielnikami liczb całkowitych o wydajności dwóch instrukcji (branch) na cykl. Widoczne powyżej dwa symetryczne potoki zmiennoprzecinkowe mogą wykonywać dwie niezależne operacje dodawania lub mnożenia, a także dwie operacje mnożenia/dodawania FP na cykl za pośrednictwem rozszerzeń wektorowych.

Czytaj też: Intel Xe-HPG i XeSS. Znamy szczegóły rdzeni Alchemist oraz alternatywy DLSS w kartach Arc

Podsystem pamięci podręcznej Gracemont sprowadza się do podwójnych potoków ładowania i przechowywania, obsługujących jednoczesną przepustowość odczytu i zapisu 32 KB.

Pamięć podręczna L2 o pojemności 2 MB w procesorach konsumenckich (4 w serwerowych) jest współdzielona przez wszystkie cztery rdzenie, zapewniając 64 bajtów przepustowości odczytu na cykl przy 17 cyklach opóźnienia.