Powstał europejski procesor EPAC na bazie RISC-V, wstępne testy już rozpoczęto

Na samym początku należy wyjaśnić, czym dokładnie jest European Processor Initiative, zrzeszający 28 partnerów z 10 krajów europejskich. Ten projekt ma na celu stworzenie przeznaczonych specjalnie dla Unii Europejskiej procesorów oraz technologii, które umożliwią jej stanie się niezależną od tej zagranicznej. Nie jest to łatwe zwłaszcza przez to, że dąży się obecnie do stworzenia całkowicie niestandardowego sprzętu HPC od podstaw. Ten z kolei wymaga m.in. w pełni autorskich procesorów.

Czytaj też: Projekt tranzystorów nowej generacji. Oto CasFET prosto z uniwersytetu

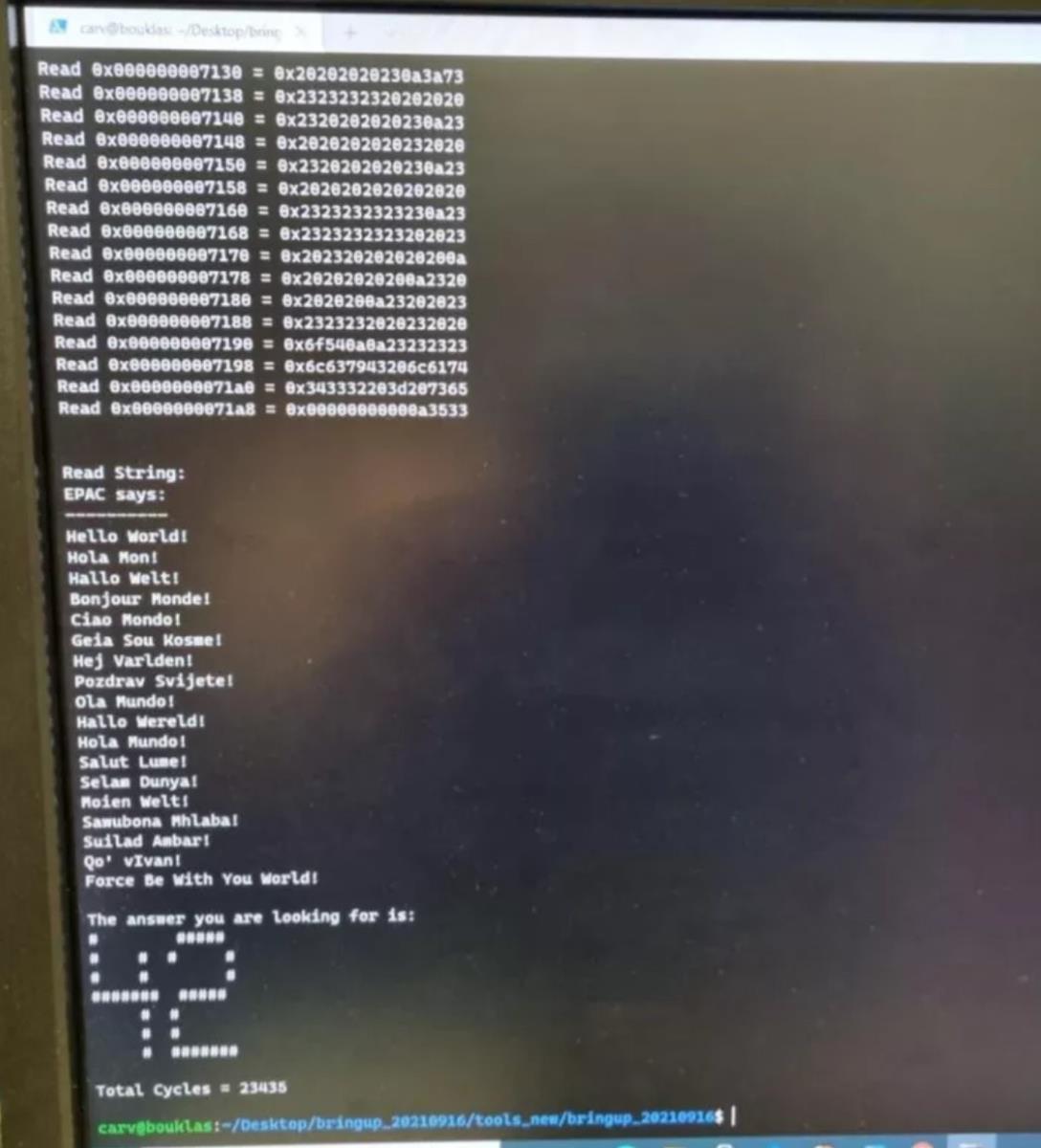

European Processor Initiative (EPI) pracuje więc obecnie nad zapewnieniem Unii Europejskiej niezależności w dziedzinie obliczeń wysokiej wydajności (HPC), a jedną z dróg ku temu, jest opracowanie niestandardowych akceleratorów opartych na RISC-V. To zresztą właśnie zrobiono, czego owocem jest European Processor Accelerator (EPAC), który został zaprojektowany z myślą o “wysokiej wydajności i wysokiej przepustowości obliczeń”.

Jednym z kluczowych segmentów działań EPI jest opracowanie i zademonstrowanie w pełni rozwiniętych w Europie procesorów opartych na architekturze zestawu instrukcji RISC-V, zapewniających energooszczędne i wysokowydajne rdzenie akceleratorów o nazwie EPAC (European Processor Accelerators)– czytamy w ogłoszeniu EPI.

Czytaj też: Dlaczego Apple M1 jest tak wydajny? 350-stronicowy dokument próbuje to wyjaśnić

Dziś dowiedzieliśmy się, że ponoć pierwsze egzemplarze EPAC z wykorzystaniem 22 nm procesu FDX Global Foundries już powstały i obecnie są testowane w laboratoriach EPI. Ich powierzchnia mierzy 26,97 mm kwadratowych, a na ten moment przyjmują formę pakietu testowego FCBGA z kulkami lutowniczymi 22 x 22 w układzie siatki i chipem o częstotliwości docelowej na poziomie 1 GHz.

Czytaj też: Szanse na tanie panele słoneczne. Oto najwydajniejsze na świecie ogniwo słoneczne bez srebra

Składają się na nie cztery matryce VPU (Vector Processing Units), bazujące na rdzeniu Avispado zaprojektowanym przez SemiDynamics oraz elemeny przetwarzania wektorów, za których opracowanie odpowiada chorwacki uniwersytet w Zagrzebiu i Barcelońskie Centrum Superkomputerowe. Z kolei każda matryca posiada węzły macierzyste, pamięć podręczną L2, akceleratory Stencil i Tensor oraz procesor z myślą o obliczeniach zmiennej precyzji (VRP). Wszystkie te komponenty łączy Network-on-Chip.